泰拉瑞亚电路:三种乘法器原理讲解,泰拉瑞亚乘法器怎么做?

发表时间: 2023-05-21 09:35:26

最后更新: 2023-05-21 09:35:26(2年前)

Tips:本文最近1个月没有更新,如果内容错误、缺失的话,你可以在评论区留言 (๑•̀ㅂ•́)و✧--0

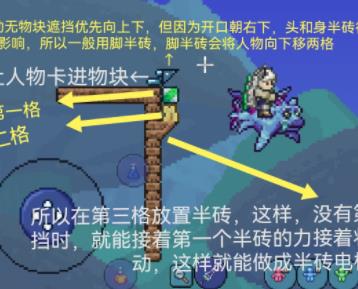

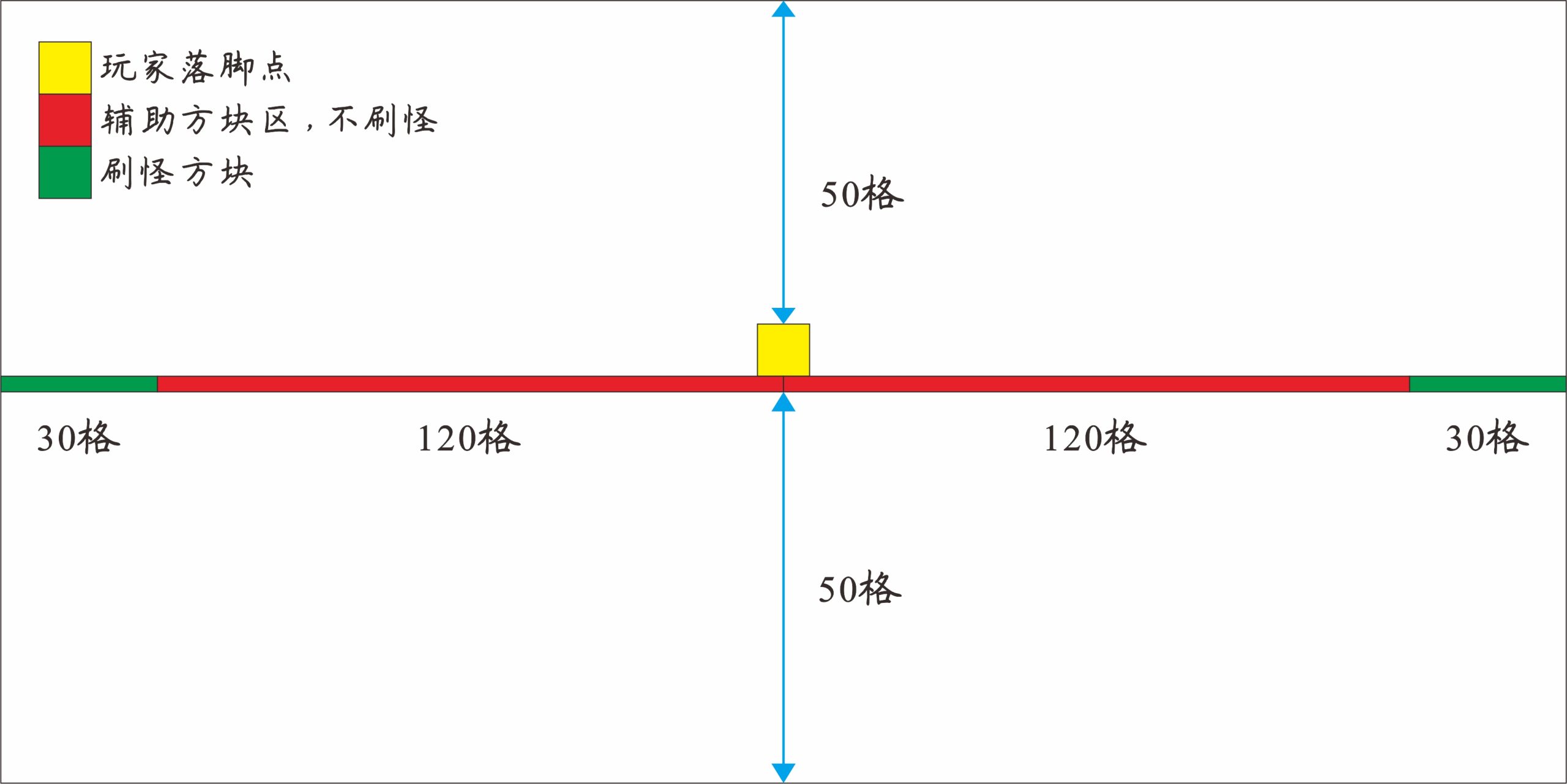

1.行波进位乘法器(单周期) 乘法是加法的推广,乘法器也是加法器的推广。我们首先来看二进制乘法的竖式计 算。因为乘法规模较大,这里给出 4 位乘法的例子。来自@熵增

发表于:泰拉技术协会

原帖地址:电路:三种乘法器原理讲解

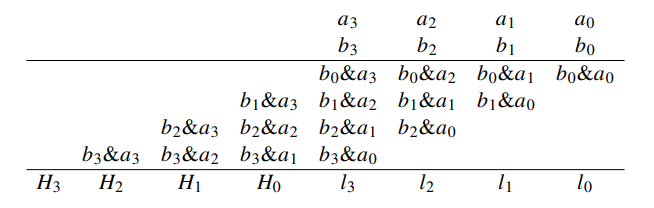

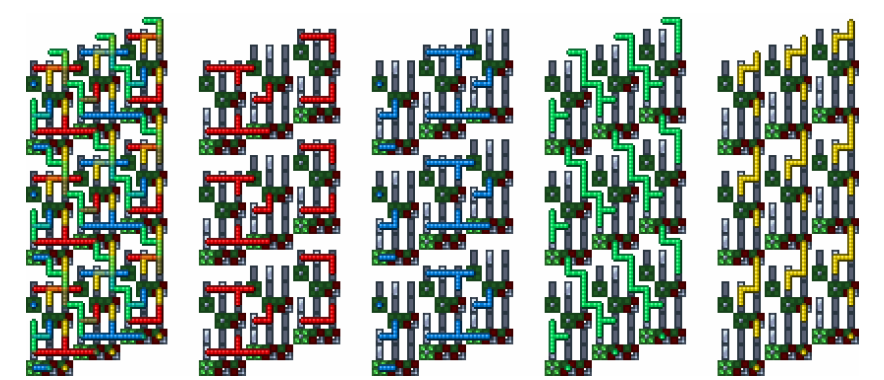

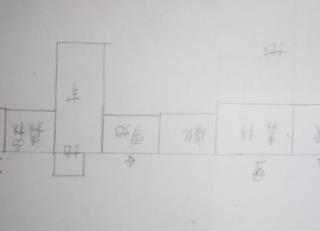

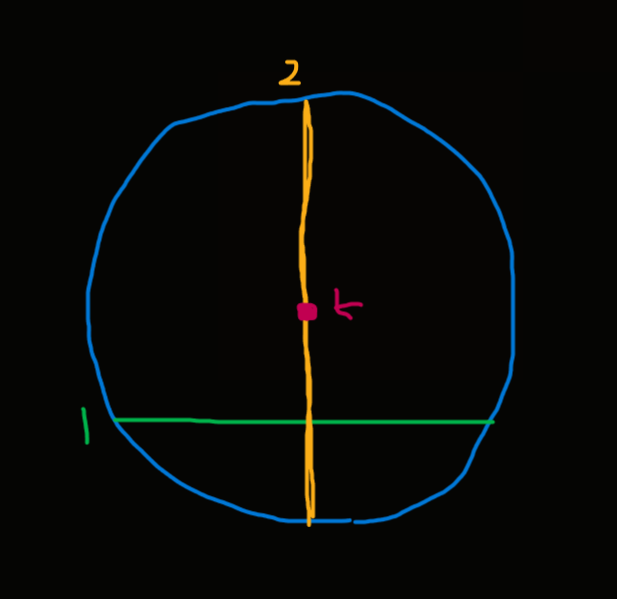

乘法竖式计算

从上图可以看出来,做一个 4 位乘法实际上就是做 4 个数的加法。4 个数的加法,

可以按照运算顺序拆分成三次 2 个数的加法,如下图所示。

乘法竖式计算

从上图可以看出来,做一个 4 位乘法实际上就是做 4 个数的加法。4 个数的加法,

可以按照运算顺序拆分成三次 2 个数的加法,如下图所示。

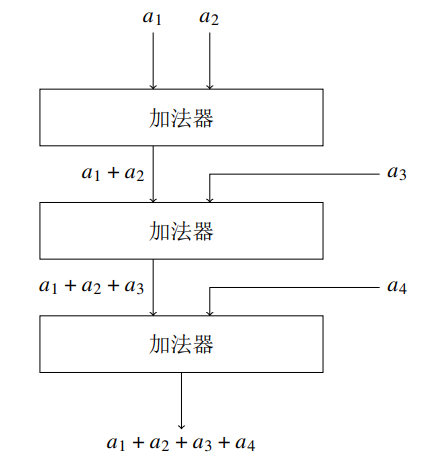

四个加数 𝑎1, 𝑎2, 𝑎3, 𝑎4 连加

把之前贴子中的加法器展开成串联的全加器,就得到了四位乘法器的结构示意图。

四个加数 𝑎1, 𝑎2, 𝑎3, 𝑎4 连加

把之前贴子中的加法器展开成串联的全加器,就得到了四位乘法器的结构示意图。

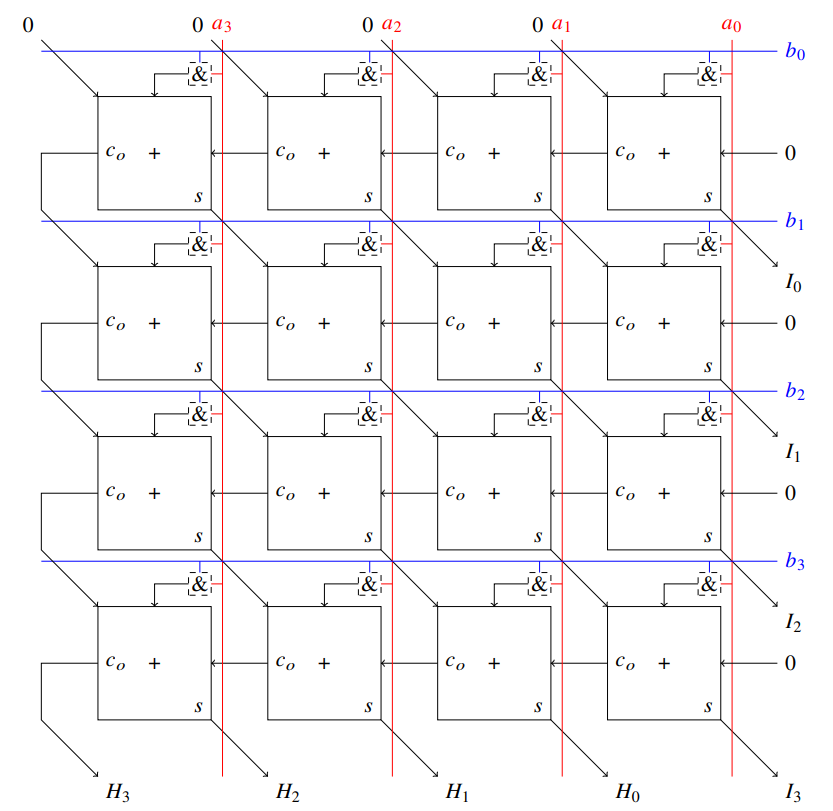

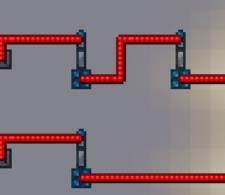

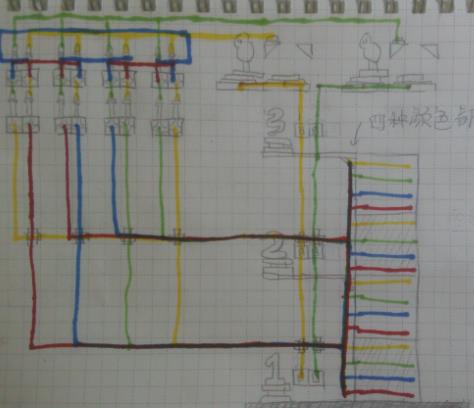

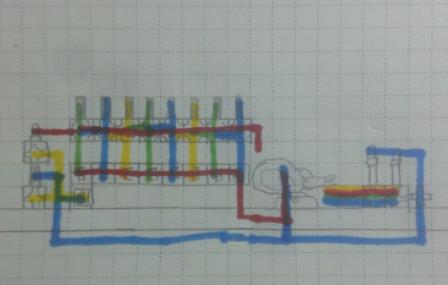

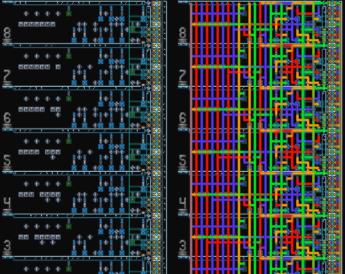

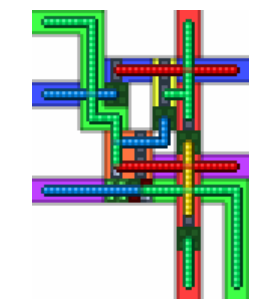

四位乘法器结构示意图。大的实线方框表示全加器,𝑐𝑜 表示进位输出,𝑠 表示和输出。小

的虚线方框表示与门,红蓝线输入,黑线输出。两个乘数分别从上方和右方输入,乘积的低位从

右边输出,高位从下边输出。全加器缺少的输入补零。左右相邻的两个全加器,右边的早一个逻

辑帧;上下相邻的两个全加器,上边的早两个逻辑帧。

四位乘法器结构示意图。大的实线方框表示全加器,𝑐𝑜 表示进位输出,𝑠 表示和输出。小

的虚线方框表示与门,红蓝线输入,黑线输出。两个乘数分别从上方和右方输入,乘积的低位从

右边输出,高位从下边输出。全加器缺少的输入补零。左右相邻的两个全加器,右边的早一个逻

辑帧;上下相邻的两个全加器,上边的早两个逻辑帧。

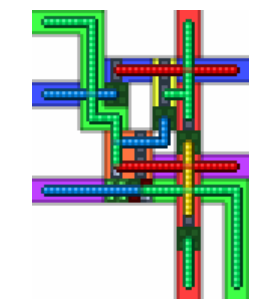

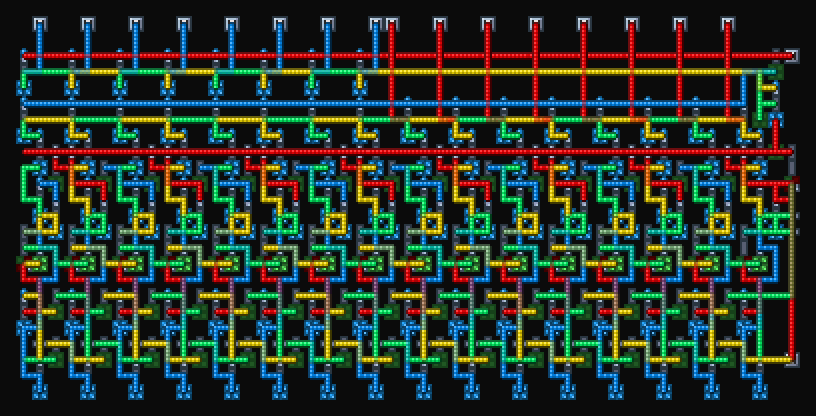

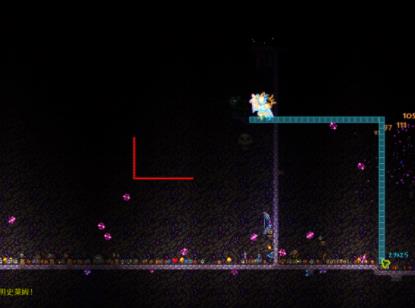

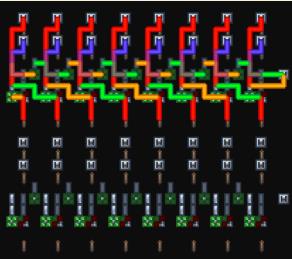

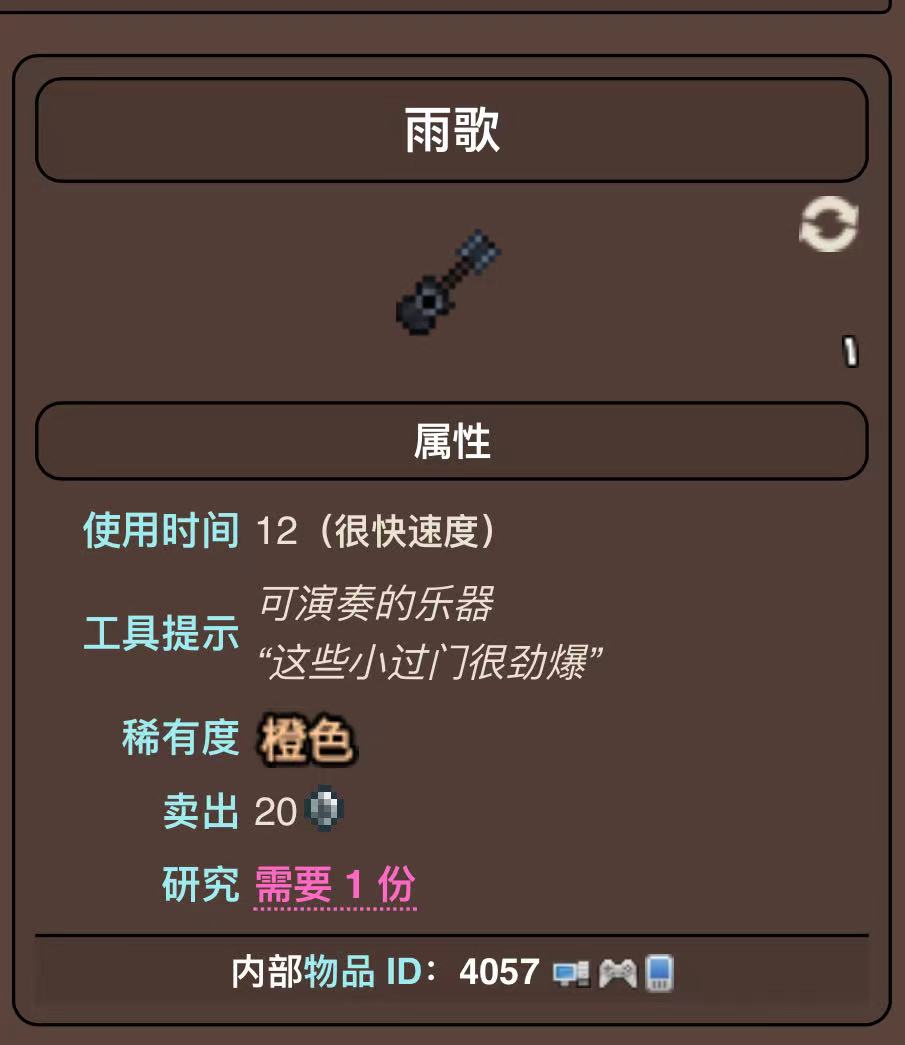

乘法器单个单元的结构

其中用不同颜色的背景墙标记区域和线路。橙色区域为全加器。黄色区域是与门。蓝色线路是从右边输入的乘数,每经过一个单元要延迟 1 个逻辑帧。红色线路是从上边输入的乘数,每经过一个单元要延迟 2 个逻辑帧。紫色线路是横向的进位传递。绿色线路是从左上到右下的和传递。

乘法器单个单元的结构

其中用不同颜色的背景墙标记区域和线路。橙色区域为全加器。黄色区域是与门。蓝色线路是从右边输入的乘数,每经过一个单元要延迟 1 个逻辑帧。红色线路是从上边输入的乘数,每经过一个单元要延迟 2 个逻辑帧。紫色线路是横向的进位传递。绿色线路是从左上到右下的和传递。

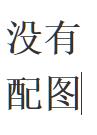

堆叠优化后的效果

其中每个单元大小 3*7。优化过程用到了如下的接线

技巧:

-左右方向上红蓝线循环,便于接线。

-相邻两列错位,便于进位和横向乘数的传递。

-纵向的逻辑延迟用到了一个异或门,从而这个门不需要为经过的绿线让路。

-与门利用了等式 𝑎&𝑏 = ˜𝑎𝑏&𝑏,便于接线。

2.移位相加乘法器(多周期)

堆叠优化后的效果

其中每个单元大小 3*7。优化过程用到了如下的接线

技巧:

-左右方向上红蓝线循环,便于接线。

-相邻两列错位,便于进位和横向乘数的传递。

-纵向的逻辑延迟用到了一个异或门,从而这个门不需要为经过的绿线让路。

-与门利用了等式 𝑎&𝑏 = ˜𝑎𝑏&𝑏,便于接线。

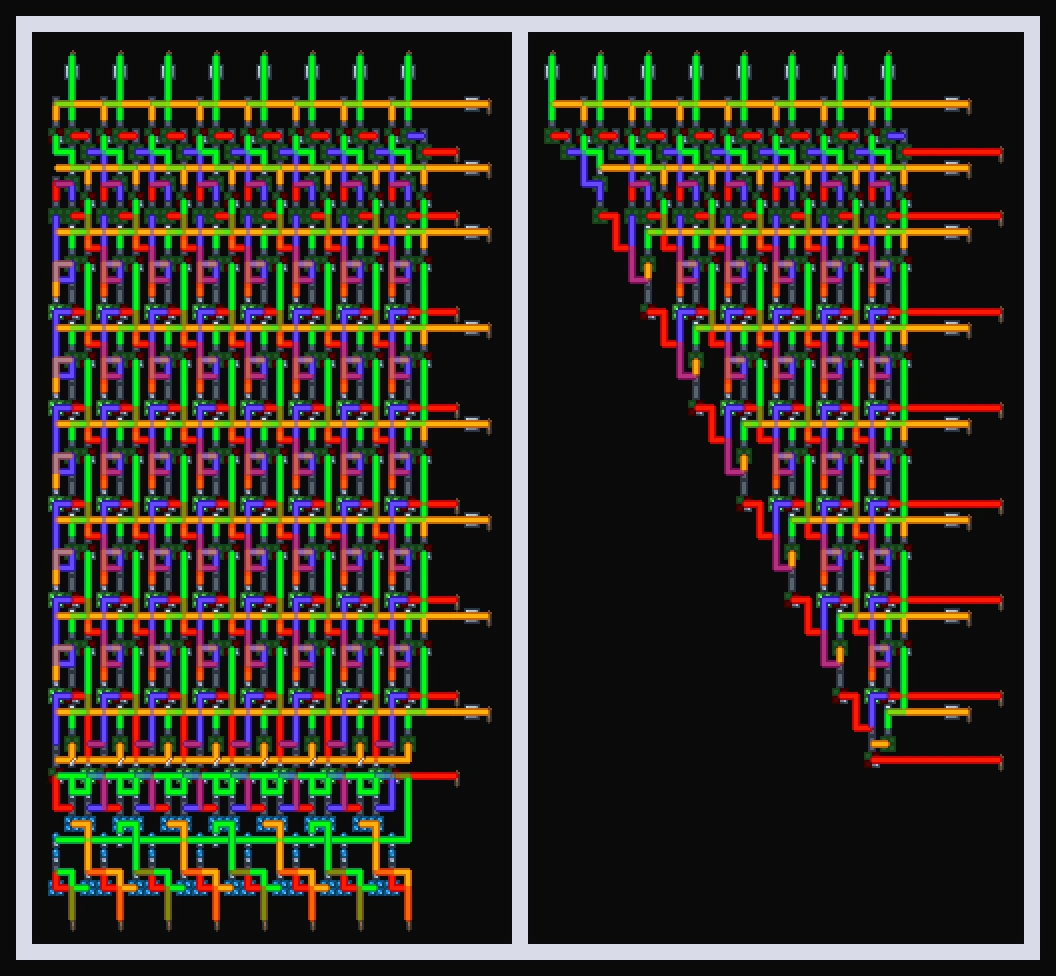

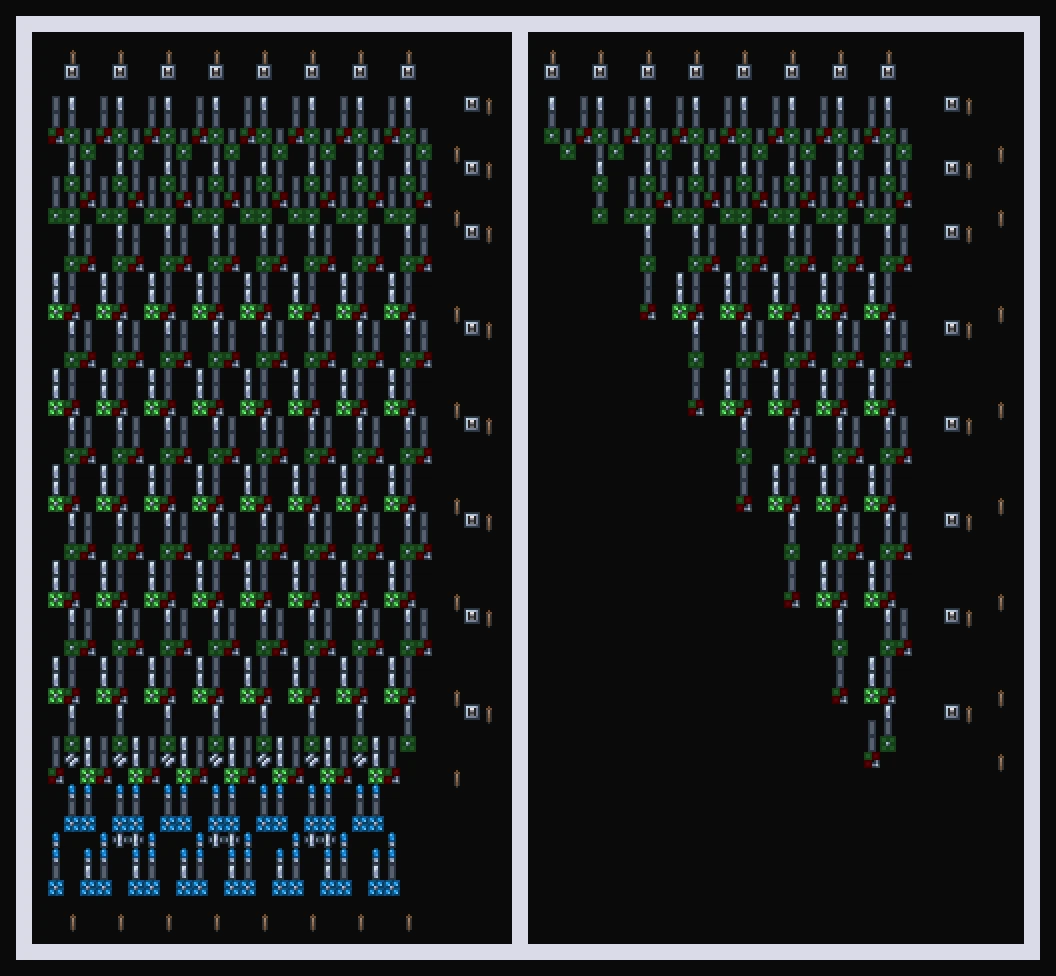

2.移位相加乘法器(多周期)

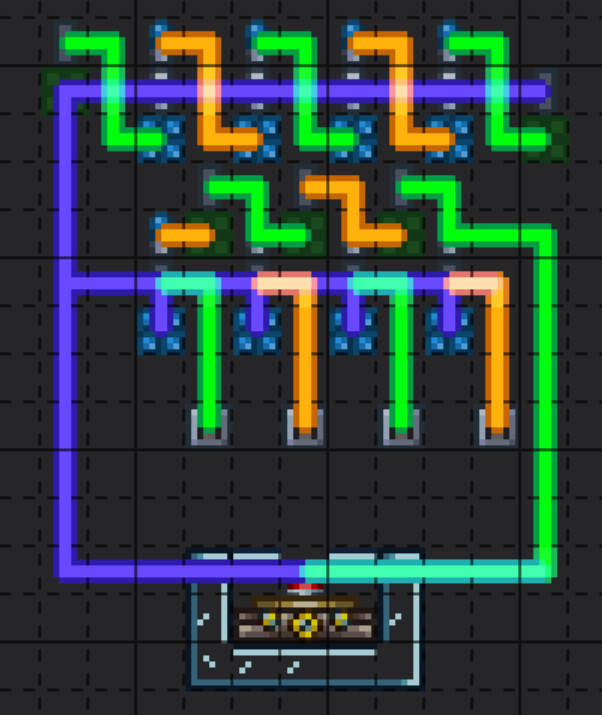

与前述单周期乘法器原理相同,但是使用驱动复用相同电路以减少面积,计算n位乘法需要n周期。

3.保存进位乘法器(单周期)

与前述单周期乘法器原理相同,但是使用驱动复用相同电路以减少面积,计算n位乘法需要n周期。

3.保存进位乘法器(单周期)

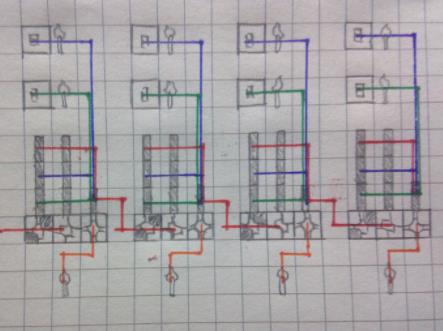

使用保留进位加法器(Carry Save Adder,CSA)代替行波进位加法器(Ripple Carry Adder,RCA)以减少面积。就单元面积来看仍然是3*7,但连接后呈矩形,不像行波进位乘法器呈平行四边形。矩形的模块较容易与其他模块配合使用。注意到下方使用并行输入串行输出的累加器代替行波进位加法器以减少面积,所以这是一个用时序逻辑部件模拟组合逻辑部件的电路。这是目前最小的单周期乘法器。

4.展望

多周期乘法器仍有压缩的空间,但使用通用的ALU代替专用的乘法器和除法器等模块显然是更好的选择。而按照现在原理的单周期乘法器可能已经压缩到了极限,继续压缩也不会有大幅的面积减少,所以可能需要提出新的原理来进一步压缩,比如使用booth编码或Wallace tree进一步压缩。但基于泰拉电路的特性,可能并不合适。

使用保留进位加法器(Carry Save Adder,CSA)代替行波进位加法器(Ripple Carry Adder,RCA)以减少面积。就单元面积来看仍然是3*7,但连接后呈矩形,不像行波进位乘法器呈平行四边形。矩形的模块较容易与其他模块配合使用。注意到下方使用并行输入串行输出的累加器代替行波进位加法器以减少面积,所以这是一个用时序逻辑部件模拟组合逻辑部件的电路。这是目前最小的单周期乘法器。

4.展望

多周期乘法器仍有压缩的空间,但使用通用的ALU代替专用的乘法器和除法器等模块显然是更好的选择。而按照现在原理的单周期乘法器可能已经压缩到了极限,继续压缩也不会有大幅的面积减少,所以可能需要提出新的原理来进一步压缩,比如使用booth编码或Wallace tree进一步压缩。但基于泰拉电路的特性,可能并不合适。

泰拉瑞亚boss史莱姆王怎么召唤 屎王详细攻略技巧

泰拉瑞亚boss史莱姆王怎么召唤 屎王详细攻略技巧

泰拉瑞亚boss蜂王怎么召唤 蜂王掉落物品及详细攻略

泰拉瑞亚boss蜂王怎么召唤 蜂王掉落物品及详细攻略

泰拉瑞亚克苏鲁之眼怎么召唤 泰拉瑞亚boss克苏鲁之眼攻略

泰拉瑞亚克苏鲁之眼怎么召唤 泰拉瑞亚boss克苏鲁之眼攻略

泰拉瑞亚专家模式肉山怎么打 泰拉瑞亚boss肉山打法和掉落详解

泰拉瑞亚专家模式肉山怎么打 泰拉瑞亚boss肉山打法和掉落详解

泰拉瑞亚克苏鲁之脑怎么召唤 专家模式boss克苏鲁之脑怎么打

泰拉瑞亚克苏鲁之脑怎么召唤 专家模式boss克苏鲁之脑怎么打

泰拉瑞亚双子魔眼怎么召唤 boss双子魔眼怎么打

泰拉瑞亚双子魔眼怎么召唤 boss双子魔眼怎么打

泰拉瑞亚世纪之花在哪 泰拉瑞亚boss世纪之花怎么打

泰拉瑞亚世纪之花在哪 泰拉瑞亚boss世纪之花怎么打

泰拉瑞亚石巨人掉落详解攻略 泰拉瑞亚boss石头人怎么打

泰拉瑞亚石巨人掉落详解攻略 泰拉瑞亚boss石头人怎么打

泰拉瑞亚猪鲨公爵掉落 泰拉瑞亚boss猪龙鱼公爵详细攻略

泰拉瑞亚猪鲨公爵掉落 泰拉瑞亚boss猪龙鱼公爵详细攻略

泰拉瑞亚boss月球领主怎么打 专家模式月总掉落详细攻略

泰拉瑞亚boss月球领主怎么打 专家模式月总掉落详细攻略

泰拉瑞亚黑魔法师武器 泰拉瑞亚boss黑魔法师掉落打法详解

泰拉瑞亚黑魔法师武器 泰拉瑞亚boss黑魔法师掉落打法详解

泰拉瑞亚飞翔的荷兰人号怎么打 泰拉瑞亚boss荷兰海盗船掉落

泰拉瑞亚飞翔的荷兰人号怎么打 泰拉瑞亚boss荷兰海盗船掉落

泰拉瑞亚boss食人魔怎么打 泰拉瑞亚食人魔属性掉落详解

泰拉瑞亚boss食人魔怎么打 泰拉瑞亚食人魔属性掉落详解

泰拉瑞亚万圣节树妖怎么打 泰拉瑞亚南瓜月哀木攻略

泰拉瑞亚万圣节树妖怎么打 泰拉瑞亚南瓜月哀木攻略

泰拉瑞亚boss南瓜王攻略 泰拉瑞亚南瓜王属性掉落详解

泰拉瑞亚boss南瓜王攻略 泰拉瑞亚南瓜王属性掉落详解

泰拉瑞亚boss尖叫圣诞树怎么打 霜月圣诞树妖掉落属性详解

泰拉瑞亚boss尖叫圣诞树怎么打 霜月圣诞树妖掉落属性详解

泰拉瑞亚boss圣诞坦克怎么打 泰拉瑞亚圣诞老人坦克属性掉落详解

泰拉瑞亚boss圣诞坦克怎么打 泰拉瑞亚圣诞老人坦克属性掉落详解

泰拉瑞亚boss冰雪女王属性掉落详解 泰拉瑞亚冰霜女王咋打

泰拉瑞亚boss冰雪女王属性掉落详解 泰拉瑞亚冰霜女王咋打

泰拉瑞亚双足翼龙在哪 泰拉瑞亚boss双足翼龙掉落属性攻略

泰拉瑞亚双足翼龙在哪 泰拉瑞亚boss双足翼龙掉落属性攻略

泰拉瑞亚火星飞碟详细介绍 泰拉瑞亚boss外星人飞碟掉落

泰拉瑞亚火星飞碟详细介绍 泰拉瑞亚boss外星人飞碟掉落

泰拉瑞亚四柱怎么打 泰拉瑞亚专家模式boss天界塔顺序掉落一览

泰拉瑞亚四柱怎么打 泰拉瑞亚专家模式boss天界塔顺序掉落一览

泰拉瑞亚永夜之刃怎么合成 泰拉瑞亚永夜之刃怎么样

泰拉瑞亚永夜之刃怎么合成 泰拉瑞亚永夜之刃怎么样

泰拉瑞亚草薙剑怎么做 泰拉瑞亚草剑介绍及获得方式

泰拉瑞亚草薙剑怎么做 泰拉瑞亚草剑介绍及获得方式

泰拉瑞亚养蜂人怎么获得 泰拉瑞亚养蜂人武器武器详解

泰拉瑞亚养蜂人怎么获得 泰拉瑞亚养蜂人武器武器详解

泰拉瑞亚附魔剑怎么拿 泰拉瑞亚石中剑的位置在哪里

泰拉瑞亚附魔剑怎么拿 泰拉瑞亚石中剑的位置在哪里

泰拉瑞亚彩虹猫之刃怎么获得 泰拉瑞亚猫咪之刃怎么做

泰拉瑞亚彩虹猫之刃怎么获得 泰拉瑞亚猫咪之刃怎么做

泰拉瑞亚星辰之怒怎么获得 泰拉瑞亚武器狂星之怒属性介绍

泰拉瑞亚星辰之怒怎么获得 泰拉瑞亚武器狂星之怒属性介绍

泰拉瑞亚波涌之刃怎么获得 泰拉瑞亚波动之刃属性介绍

泰拉瑞亚波涌之刃怎么获得 泰拉瑞亚波动之刃属性介绍

泰拉瑞亚泰拉刃怎么合成 泰拉瑞亚泰拉之刃属性详解

泰拉瑞亚泰拉刃怎么合成 泰拉瑞亚泰拉之刃属性详解

泰拉瑞亚原版永夜刃合成方法 泰拉瑞亚真永夜之刃怎么获得

泰拉瑞亚原版永夜刃合成方法 泰拉瑞亚真永夜之刃怎么获得

泰拉瑞亚原版断钢剑怎么获得 泰拉瑞亚真奥钢剑属性详解

泰拉瑞亚原版断钢剑怎么获得 泰拉瑞亚真奥钢剑属性详解

泰拉瑞亚圣诞树剑怎么获得 泰拉瑞亚武器圣诞树剑属性详解

泰拉瑞亚圣诞树剑怎么获得 泰拉瑞亚武器圣诞树剑属性详解

泰拉瑞亚无头骑士之刃怎么获得 泰拉瑞亚无头骑士剑属性详解

泰拉瑞亚无头骑士之刃怎么获得 泰拉瑞亚无头骑士剑属性详解

泰拉瑞亚飞龙巨刃怎么获得 泰拉瑞亚飞龙之刃属性详解

泰拉瑞亚飞龙巨刃怎么获得 泰拉瑞亚飞龙之刃属性详解

泰拉瑞亚惊魂刀怎么获得 泰拉瑞亚隐身时加伤害的变态刀

泰拉瑞亚惊魂刀怎么获得 泰拉瑞亚隐身时加伤害的变态刀

泰拉瑞亚游戏中最强的悠悠球 泰拉瑞亚泰拉悠悠球怎么合成

泰拉瑞亚游戏中最强的悠悠球 泰拉瑞亚泰拉悠悠球怎么合成

泰拉瑞亚北极矛怎么得 泰拉瑞亚雪人北极矛属性详解

泰拉瑞亚北极矛怎么得 泰拉瑞亚雪人北极矛属性详解

泰拉瑞亚破晓之光怎么合成 泰拉瑞亚破晓黎明武器属性ID详情

泰拉瑞亚破晓之光怎么合成 泰拉瑞亚破晓黎明武器属性ID详情

泰拉瑞亚日耀喷发剑怎么获得 泰拉瑞亚太阳能喷发属性详解

泰拉瑞亚日耀喷发剑怎么获得 泰拉瑞亚太阳能喷发属性详解

泰拉瑞亚天龙之怒武器属性详解 泰拉瑞亚天空龙之怒怎么获得

泰拉瑞亚天龙之怒武器属性详解 泰拉瑞亚天空龙之怒怎么获得

泰拉瑞亚血月怎么召唤 泰拉瑞亚血月之夜攻略详解

泰拉瑞亚血月怎么召唤 泰拉瑞亚血月之夜攻略详解

泰拉瑞亚怎么召唤哥布林入侵 泰拉瑞亚哥布林军队事件攻略

泰拉瑞亚怎么召唤哥布林入侵 泰拉瑞亚哥布林军队事件攻略

泰拉瑞亚史莱姆雨怎么召唤 泰拉瑞亚史莱姆从天而降是什么意思

泰拉瑞亚史莱姆雨怎么召唤 泰拉瑞亚史莱姆从天而降是什么意思

泰拉瑞亚派对有什么用 泰拉瑞亚派对事件详解

泰拉瑞亚派对有什么用 泰拉瑞亚派对事件详解

泰拉瑞亚沙尘暴天气事件攻略 泰拉瑞亚沙尘暴事件怎么触发

泰拉瑞亚沙尘暴天气事件攻略 泰拉瑞亚沙尘暴事件怎么触发

泰拉瑞亚远古军团怎么召唤 泰拉瑞亚撒旦军队入侵详细攻略

泰拉瑞亚远古军团怎么召唤 泰拉瑞亚撒旦军队入侵详细攻略

泰拉瑞亚雪人军团怎么召唤 泰拉瑞亚雪人军团事件详细攻略

泰拉瑞亚雪人军团怎么召唤 泰拉瑞亚雪人军团事件详细攻略

泰拉瑞亚日食怎么召唤 泰拉瑞亚日食时间掉落攻略详解

泰拉瑞亚日食怎么召唤 泰拉瑞亚日食时间掉落攻略详解

泰拉瑞亚海盗入侵条件 泰拉瑞亚海盗入侵掉落详解

泰拉瑞亚海盗入侵条件 泰拉瑞亚海盗入侵掉落详解

泰拉瑞亚南瓜月怎么召唤 泰拉瑞亚南瓜月事件怎么打详细攻略

泰拉瑞亚南瓜月怎么召唤 泰拉瑞亚南瓜月事件怎么打详细攻略

泰拉瑞亚霜月怎么召唤 泰拉瑞亚霜月事件打法详细攻略

泰拉瑞亚霜月怎么召唤 泰拉瑞亚霜月事件打法详细攻略

泰拉瑞亚火星人入侵怎么召唤 泰拉瑞亚火星人入侵条件详细攻略

泰拉瑞亚火星人入侵怎么召唤 泰拉瑞亚火星人入侵条件详细攻略

泰拉瑞亚月亮事件这么召唤 泰拉瑞亚月球事件详细攻略

泰拉瑞亚月亮事件这么召唤 泰拉瑞亚月球事件详细攻略

泰拉瑞亚向导怎么复活 泰拉瑞亚npc向导入住条件及作用详解

泰拉瑞亚向导怎么复活 泰拉瑞亚npc向导入住条件及作用详解

泰拉瑞亚商人怎么入住 泰拉瑞亚商人被杀死怎么办

泰拉瑞亚商人怎么入住 泰拉瑞亚商人被杀死怎么办

泰拉瑞亚护士入住条件 泰拉瑞亚护士作用介绍

泰拉瑞亚护士入住条件 泰拉瑞亚护士作用介绍

泰拉瑞亚油漆工入住条件 泰拉瑞亚油漆工的作用详解

泰拉瑞亚油漆工入住条件 泰拉瑞亚油漆工的作用详解

泰拉瑞亚染料商人入驻条件 泰拉瑞亚NPC染料商左右介绍

泰拉瑞亚染料商人入驻条件 泰拉瑞亚NPC染料商左右介绍

泰拉瑞亚派对女孩入住条件 泰拉瑞亚派对女孩作用是什么

泰拉瑞亚派对女孩入住条件 泰拉瑞亚派对女孩作用是什么

泰拉瑞亚发型师入住条件 泰拉瑞亚发型师作用介绍

泰拉瑞亚发型师入住条件 泰拉瑞亚发型师作用介绍

泰拉瑞亚爆破专家死了怎么办 泰拉瑞亚NPC爆破专家入驻条件

泰拉瑞亚爆破专家死了怎么办 泰拉瑞亚NPC爆破专家入驻条件

泰拉瑞亚树妖NPC入住条件介绍 泰拉瑞亚树妖祝福是什么

泰拉瑞亚树妖NPC入住条件介绍 泰拉瑞亚树妖祝福是什么

泰拉瑞亚酒馆老板副本攻略 泰拉瑞亚酒馆老板死了怎么办

泰拉瑞亚酒馆老板副本攻略 泰拉瑞亚酒馆老板死了怎么办

泰拉瑞亚军火商人在哪 泰拉瑞亚npc军火商入驻条件及介绍

泰拉瑞亚军火商人在哪 泰拉瑞亚npc军火商入驻条件及介绍

泰拉瑞亚哥布林工匠怎么找 泰拉瑞亚哥布林工匠在哪里攻略

泰拉瑞亚哥布林工匠怎么找 泰拉瑞亚哥布林工匠在哪里攻略

泰拉瑞亚巫医入住条件 泰拉瑞亚NPC巫医怎么召唤详细攻略

泰拉瑞亚巫医入住条件 泰拉瑞亚NPC巫医怎么召唤详细攻略

泰拉瑞亚服装商人巫毒娃娃有什么用 泰拉瑞亚NPC服装商入住条件攻略

泰拉瑞亚服装商人巫毒娃娃有什么用 泰拉瑞亚NPC服装商入住条件攻略

泰拉瑞亚机械师在哪里 泰拉瑞亚工程师入驻条件详解

泰拉瑞亚机械师在哪里 泰拉瑞亚工程师入驻条件详解

泰拉瑞亚税收官有什么用 泰拉瑞亚税收官在地狱怎么上来

泰拉瑞亚税收官有什么用 泰拉瑞亚税收官在地狱怎么上来

泰拉瑞亚海盗npc有什么用 泰拉瑞亚海盗npc怎么入驻

泰拉瑞亚海盗npc有什么用 泰拉瑞亚海盗npc怎么入驻

泰拉瑞亚蘑菇人入住条件 泰拉瑞亚NPC松露人卖什么详细攻略

泰拉瑞亚蘑菇人入住条件 泰拉瑞亚NPC松露人卖什么详细攻略

泰拉瑞亚巫师入住条件 泰拉瑞亚巫师NPC的作用详解

泰拉瑞亚巫师入住条件 泰拉瑞亚巫师NPC的作用详解

泰拉瑞亚蒸汽朋克人入住条件 泰拉瑞亚蒸汽朋克人NPC卖什么

泰拉瑞亚蒸汽朋克人入住条件 泰拉瑞亚蒸汽朋克人NPC卖什么

泰拉瑞亚机器侠npc有什么用 泰拉瑞亚机器侠入住条件详细介绍

泰拉瑞亚机器侠npc有什么用 泰拉瑞亚机器侠入住条件详细介绍

泰拉瑞亚圣诞老人入住条件 泰拉瑞亚圣诞老人npc出售物品详细介绍

泰拉瑞亚圣诞老人入住条件 泰拉瑞亚圣诞老人npc出售物品详细介绍

泰拉瑞亚旅商到达条件 泰拉瑞亚旅商NPC已死去是什么意思

泰拉瑞亚旅商到达条件 泰拉瑞亚旅商NPC已死去是什么意思

泰拉瑞亚老人入住条件 泰拉瑞亚老人的诅咒npc介绍攻略

泰拉瑞亚老人入住条件 泰拉瑞亚老人的诅咒npc介绍攻略

泰拉瑞亚骷髅商人在哪 泰拉瑞亚骷髅商人无眼威利怎么入驻

泰拉瑞亚骷髅商人在哪 泰拉瑞亚骷髅商人无眼威利怎么入驻

泰拉瑞亚工作台合成表 泰拉瑞亚工作台怎么用

泰拉瑞亚工作台合成表 泰拉瑞亚工作台怎么用

泰拉瑞亚远古工作台有什么用 泰拉瑞亚远古操纵机合成表大全

泰拉瑞亚远古工作台有什么用 泰拉瑞亚远古操纵机合成表大全

泰拉瑞亚精金熔炉怎么合成 泰拉瑞亚精金熔炉合成表大全

泰拉瑞亚精金熔炉怎么合成 泰拉瑞亚精金熔炉合成表大全

泰拉瑞亚自动锤炼机怎么获得 泰拉瑞亚自动锤炼机怎么使用

泰拉瑞亚自动锤炼机怎么获得 泰拉瑞亚自动锤炼机怎么使用

泰拉瑞亚书架怎么做 泰拉瑞亚书架有什么用

泰拉瑞亚书架怎么做 泰拉瑞亚书架有什么用

泰拉瑞亚骨头焊接机有什么用 泰拉瑞亚骨头焊机怎么获得

泰拉瑞亚骨头焊接机有什么用 泰拉瑞亚骨头焊机怎么获得

泰拉瑞亚搅拌机什么用 泰拉瑞亚搅拌机沥青合成表

泰拉瑞亚搅拌机什么用 泰拉瑞亚搅拌机沥青合成表

泰拉瑞亚基本物品合成表 泰拉瑞亚空手可以合成的物品大全

泰拉瑞亚基本物品合成表 泰拉瑞亚空手可以合成的物品大全

泰拉瑞亚烹饪锅合成表 泰拉瑞亚大锅有什么用

泰拉瑞亚烹饪锅合成表 泰拉瑞亚大锅有什么用

泰拉瑞亚水晶球能做什么 泰拉瑞亚水晶球合成表大全

泰拉瑞亚水晶球能做什么 泰拉瑞亚水晶球合成表大全

泰拉瑞亚恶魔祭坛在哪里 泰拉瑞亚猩红祭坛合成表大全

泰拉瑞亚恶魔祭坛在哪里 泰拉瑞亚猩红祭坛合成表大全

泰拉瑞亚染缸怎么获得 泰拉瑞亚染缸合成表

泰拉瑞亚染缸怎么获得 泰拉瑞亚染缸合成表

泰拉瑞亚血肉克隆台怎么获得 泰拉瑞亚血肉克隆台合成表

泰拉瑞亚血肉克隆台怎么获得 泰拉瑞亚血肉克隆台合成表

泰拉瑞亚熔炉合成表 泰拉瑞亚熔炉合成材料

泰拉瑞亚熔炉合成表 泰拉瑞亚熔炉合成材料

泰拉瑞亚玻璃窑合成表 泰拉瑞亚玻璃窑可以合成什么物品

泰拉瑞亚玻璃窑合成表 泰拉瑞亚玻璃窑可以合成什么物品

泰拉瑞亚重型工作台可以做什么 泰拉瑞亚重型工作台合成表大全

泰拉瑞亚重型工作台可以做什么 泰拉瑞亚重型工作台合成表大全

泰拉瑞亚地狱熔炉有什么用 泰拉瑞亚地狱熔炉合成表

泰拉瑞亚地狱熔炉有什么用 泰拉瑞亚地狱熔炉合成表

泰拉瑞亚蜂蜜分配机有什么 泰拉瑞亚蜂蜜分配机合成表

泰拉瑞亚蜂蜜分配机有什么 泰拉瑞亚蜂蜜分配机合成表

泰拉瑞亚冰雪机怎么获得 泰拉瑞亚冰雪机合成表大全

泰拉瑞亚冰雪机怎么获得 泰拉瑞亚冰雪机合成表大全

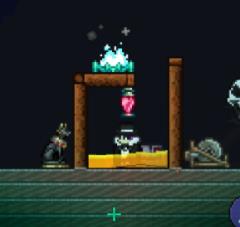

泰拉瑞亚灌注站合成表 泰拉瑞亚灌注站怎么做

泰拉瑞亚灌注站合成表 泰拉瑞亚灌注站怎么做

泰拉瑞亚铁砧怎么做 泰拉瑞亚铁砧/铅砧合成表大全

泰拉瑞亚铁砧怎么做 泰拉瑞亚铁砧/铅砧合成表大全

泰拉瑞亚丛林蜥蜴熔炉有什么用 泰拉瑞亚丛林蜥蜴熔炉合成表大全

泰拉瑞亚丛林蜥蜴熔炉有什么用 泰拉瑞亚丛林蜥蜴熔炉合成表大全

泰拉瑞亚生命木织机合成表大全 泰拉瑞亚生命木织机有什么用

泰拉瑞亚生命木织机合成表大全 泰拉瑞亚生命木织机有什么用

泰拉瑞亚织布机合成表大全 泰拉瑞亚织布机怎么做

泰拉瑞亚织布机合成表大全 泰拉瑞亚织布机怎么做

泰拉瑞亚秘银砧合成表大全 泰拉瑞亚秘银砧怎么做

泰拉瑞亚秘银砧合成表大全 泰拉瑞亚秘银砧怎么做

泰拉瑞亚山铜砧合成表大全 泰拉瑞亚山铜砧怎么做

泰拉瑞亚山铜砧合成表大全 泰拉瑞亚山铜砧怎么做

泰拉瑞亚炼药桌合成表大全 泰拉瑞亚炼药桌怎么用

泰拉瑞亚炼药桌合成表大全 泰拉瑞亚炼药桌怎么用

泰拉瑞亚锯木机有什么用 泰拉瑞亚锯木机合成表

泰拉瑞亚锯木机有什么用 泰拉瑞亚锯木机合成表

泰拉瑞亚天磨有什么用 泰拉瑞亚天磨合成表大全

泰拉瑞亚天磨有什么用 泰拉瑞亚天磨合成表大全

泰拉瑞亚固化机怎么用视频 泰拉瑞亚固化机合成表分享

泰拉瑞亚固化机怎么用视频 泰拉瑞亚固化机合成表分享

泰拉瑞亚蒸汽朋克锅炉合成表分享 泰拉瑞亚蒸汽朋克锅炉有什么用

泰拉瑞亚蒸汽朋克锅炉合成表分享 泰拉瑞亚蒸汽朋克锅炉有什么用

泰拉瑞亚桌子加椅子合成表大全 泰拉瑞亚木桌+木椅可以合成什么

泰拉瑞亚桌子加椅子合成表大全 泰拉瑞亚木桌+木椅可以合成什么

泰拉瑞亚工匠作坊配方 泰拉瑞亚工匠作坊合成表大全

泰拉瑞亚工匠作坊配方 泰拉瑞亚工匠作坊合成表大全

泰拉瑞亚工作台怎么做 泰拉瑞亚工作台合成表配方大全

泰拉瑞亚工作台怎么做 泰拉瑞亚工作台合成表配方大全

泰拉瑞亚服装商人巫毒娃娃怎么用 可以召唤肉山吗

泰拉瑞亚服装商人巫毒娃娃怎么用 可以召唤肉山吗

泰拉瑞亚粘性炸弹怎么获得 泰拉瑞亚粘性手雷有什么用

泰拉瑞亚粘性炸弹怎么获得 泰拉瑞亚粘性手雷有什么用

泰拉瑞亚炸弹怎么获得 泰拉瑞亚炸弹购买方法分享

泰拉瑞亚炸弹怎么获得 泰拉瑞亚炸弹购买方法分享

泰拉瑞亚蜜蜂手雷怎么做 泰拉瑞亚蜜蜂手榴弹怎么获得

泰拉瑞亚蜜蜂手雷怎么做 泰拉瑞亚蜜蜂手榴弹怎么获得

泰拉瑞亚快乐手榴弹有什么用 泰拉瑞亚欢乐手榴弹怎么获得

泰拉瑞亚快乐手榴弹有什么用 泰拉瑞亚欢乐手榴弹怎么获得

泰拉瑞亚弹力手榴弹怎么得 泰拉瑞亚弹性手榴弹获取方法分享

泰拉瑞亚弹力手榴弹怎么得 泰拉瑞亚弹性手榴弹获取方法分享

泰拉瑞亚手榴弹咋做 泰拉瑞亚手榴弹会炸到自己吗

泰拉瑞亚手榴弹咋做 泰拉瑞亚手榴弹会炸到自己吗

泰拉瑞亚弹力炸弹怎么获得 泰拉瑞亚弹力炸弹获取方法分享

泰拉瑞亚弹力炸弹怎么获得 泰拉瑞亚弹力炸弹获取方法分享

泰拉瑞亚雷管伤害是多少 泰拉瑞亚雷管怎么用

泰拉瑞亚雷管伤害是多少 泰拉瑞亚雷管怎么用

泰拉瑞亚弹力雷管怎么获得 泰拉瑞亚跳跳雷管介绍及获取方式

泰拉瑞亚弹力雷管怎么获得 泰拉瑞亚跳跳雷管介绍及获取方式

泰拉瑞亚粘性雷管怎么做 泰拉瑞亚粘性雷管获取方法介绍

泰拉瑞亚粘性雷管怎么做 泰拉瑞亚粘性雷管获取方法介绍

泰拉瑞亚炸药怎么制作 泰拉瑞亚炸药的作用获取方法分享

泰拉瑞亚炸药怎么制作 泰拉瑞亚炸药的作用获取方法分享

泰拉瑞亚毒刺矢怎么获得 泰拉瑞亚毒刺箭毒刺弹怎么合成

泰拉瑞亚毒刺矢怎么获得 泰拉瑞亚毒刺箭毒刺弹怎么合成

泰拉瑞亚地雷怎么买 泰拉瑞亚地雷阵教程

泰拉瑞亚地雷怎么买 泰拉瑞亚地雷阵教程

泰拉瑞亚爆炸杰克南瓜灯怎么用 泰拉瑞亚爆炸杰克南瓜灯获得方式

泰拉瑞亚爆炸杰克南瓜灯怎么用 泰拉瑞亚爆炸杰克南瓜灯获得方式

泰拉瑞亚火箭弹大全 泰拉瑞亚火箭弹核弹制作方法分享

泰拉瑞亚火箭弹大全 泰拉瑞亚火箭弹核弹制作方法分享

泰拉瑞亚弱效治疗药水怎么做 泰拉瑞亚弱效治疗药水介绍

泰拉瑞亚弱效治疗药水怎么做 泰拉瑞亚弱效治疗药水介绍

泰拉瑞亚治疗药水合成方式分享 泰拉瑞亚治疗药水大全

泰拉瑞亚治疗药水合成方式分享 泰拉瑞亚治疗药水大全

泰拉瑞亚强效治疗药水配方分享 泰拉瑞亚强效治疗药水可以合成什么

泰拉瑞亚强效治疗药水配方分享 泰拉瑞亚强效治疗药水可以合成什么

泰拉瑞亚超级治疗药水怎么做 泰拉瑞亚超级治疗药水配方分享

泰拉瑞亚超级治疗药水怎么做 泰拉瑞亚超级治疗药水配方分享

泰拉瑞亚蘑菇有什么用 泰拉瑞亚蘑菇可以自己种吗

泰拉瑞亚蘑菇有什么用 泰拉瑞亚蘑菇可以自己种吗

泰拉瑞亚水瓶怎么装水 泰拉瑞亚水瓶怎么合成

泰拉瑞亚水瓶怎么装水 泰拉瑞亚水瓶怎么合成

泰拉瑞亚蜂蜜瓶怎么做 泰拉瑞亚蜂蜜瓶有什么用

泰拉瑞亚蜂蜜瓶怎么做 泰拉瑞亚蜂蜜瓶有什么用

泰拉瑞亚蛋酒是什么 泰拉瑞亚蛋酒怎么获得

泰拉瑞亚蛋酒是什么 泰拉瑞亚蛋酒怎么获得

泰拉瑞亚蜂蜜鱼怎么钓 泰拉瑞亚蜂蜜鱼怎么获得

泰拉瑞亚蜂蜜鱼怎么钓 泰拉瑞亚蜂蜜鱼怎么获得

泰拉瑞亚弱效魔力药水怎么做 泰拉瑞亚弱效魔力药水怎么得

泰拉瑞亚弱效魔力药水怎么做 泰拉瑞亚弱效魔力药水怎么得

泰拉瑞亚魔力药水怎么合成 泰拉瑞亚魔力药水怎么获得

泰拉瑞亚魔力药水怎么合成 泰拉瑞亚魔力药水怎么获得

泰拉瑞亚强效魔力药水能合成什么 泰拉瑞亚强效魔力药水怎么做

泰拉瑞亚强效魔力药水能合成什么 泰拉瑞亚强效魔力药水怎么做

泰拉瑞亚超级魔力药水怎么做 泰拉瑞亚超级魔力药水怎么合成

泰拉瑞亚超级魔力药水怎么做 泰拉瑞亚超级魔力药水怎么合成

泰拉瑞亚弱效恢复药水怎么做 泰拉瑞亚弱效恢复药水怎么获得

泰拉瑞亚弱效恢复药水怎么做 泰拉瑞亚弱效恢复药水怎么获得

泰拉瑞亚恢复药水怎么做 泰拉瑞亚恢复药水合成表

泰拉瑞亚恢复药水怎么做 泰拉瑞亚恢复药水合成表

泰拉瑞亚诡药怎么得 泰拉瑞亚诡药有什么用

泰拉瑞亚诡药怎么得 泰拉瑞亚诡药有什么用

泰拉瑞亚染发剂效果分享 泰拉瑞亚染发剂的作用

泰拉瑞亚染发剂效果分享 泰拉瑞亚染发剂的作用

泰拉瑞亚变性药水有什么用 泰拉瑞亚变性药水怎么做

泰拉瑞亚变性药水有什么用 泰拉瑞亚变性药水怎么做

泰拉瑞亚虫洞药水怎么用 泰拉瑞亚虫洞药水怎么合成

泰拉瑞亚虫洞药水怎么用 泰拉瑞亚虫洞药水怎么合成

泰拉瑞亚传送药水配方是什么 泰拉瑞亚传送药水怎么合成

泰拉瑞亚传送药水配方是什么 泰拉瑞亚传送药水怎么合成

泰拉瑞亚生命水晶怎么用 泰拉瑞亚生命水晶id合成方式

泰拉瑞亚生命水晶怎么用 泰拉瑞亚生命水晶id合成方式

泰拉瑞亚生命果怎么快速得到 泰拉瑞亚生命果获取攻略

泰拉瑞亚生命果怎么快速得到 泰拉瑞亚生命果获取攻略

泰拉瑞亚魔力水晶怎么获得 泰拉瑞亚魔力水晶id怎么使用

泰拉瑞亚魔力水晶怎么获得 泰拉瑞亚魔力水晶id怎么使用

泰拉瑞亚恶魔之心怎么使用 泰拉瑞亚恶魔之心能用几次

泰拉瑞亚恶魔之心怎么使用 泰拉瑞亚恶魔之心能用几次

泰拉瑞亚弹药储备药水怎么弄 弹药储备药水怎么获得的

泰拉瑞亚弹药储备药水怎么弄 弹药储备药水怎么获得的

泰拉瑞亚箭术药水怎么做 泰拉瑞亚箭术药水对枪有用吗

泰拉瑞亚箭术药水怎么做 泰拉瑞亚箭术药水对枪有用吗

泰拉瑞亚战斗药水怎么做 泰拉瑞亚战斗药水合成表

泰拉瑞亚战斗药水怎么做 泰拉瑞亚战斗药水合成表

泰拉瑞亚魔能药水怎么做 泰拉瑞亚魔能药剂合成表

泰拉瑞亚魔能药水怎么做 泰拉瑞亚魔能药剂合成表

泰拉瑞亚暴怒药水配方合成表 泰拉瑞亚暴怒药水怎么做呢

泰拉瑞亚暴怒药水配方合成表 泰拉瑞亚暴怒药水怎么做呢

泰拉瑞亚召唤药水怎么做 泰拉瑞亚召唤药水怎么合成

泰拉瑞亚召唤药水怎么做 泰拉瑞亚召唤药水怎么合成

泰拉瑞亚泰坦药水有什么用 泰拉瑞亚泰坦药水合成方式分享

泰拉瑞亚泰坦药水有什么用 泰拉瑞亚泰坦药水合成方式分享

泰拉瑞亚怒气药水配方 泰拉瑞亚的狂暴药剂怎么样制造呢

泰拉瑞亚怒气药水配方 泰拉瑞亚的狂暴药剂怎么样制造呢

泰拉瑞亚镇静药水作用与合成方式分享

泰拉瑞亚镇静药水作用与合成方式分享

泰拉瑞亚耐力药水怎么合成 耐力药水有什么用

泰拉瑞亚耐力药水怎么合成 耐力药水有什么用

泰拉瑞亚拾心药水怎么做 泰拉瑞亚拾心药水有什么用

泰拉瑞亚拾心药水怎么做 泰拉瑞亚拾心药水有什么用

泰拉瑞亚狱火药水怎么合成 泰拉瑞亚地狱降临药水合成方式

泰拉瑞亚狱火药水怎么合成 泰拉瑞亚地狱降临药水合成方式

泰拉瑞亚隐身药水有什么用 泰拉瑞亚隐身药水怎么合成

泰拉瑞亚隐身药水有什么用 泰拉瑞亚隐身药水怎么合成

泰拉瑞亚铁皮药水合成表 泰拉瑞亚铁皮药剂怎么做

泰拉瑞亚铁皮药水合成表 泰拉瑞亚铁皮药剂怎么做

泰拉瑞亚生命力药水合成方式 泰拉瑞亚生命力药剂怎么获得

泰拉瑞亚生命力药水合成方式 泰拉瑞亚生命力药剂怎么获得

泰拉瑞亚魔力再生药水怎么做 泰拉瑞亚魔力再生药水合成表分享

泰拉瑞亚魔力再生药水怎么做 泰拉瑞亚魔力再生药水合成表分享

泰拉瑞亚再生药水合成方式 泰拉瑞亚再生药水怎么做

泰拉瑞亚再生药水合成方式 泰拉瑞亚再生药水怎么做

泰拉瑞亚荆棘药水怎么做 荆棘药水能反弹多少伤害

泰拉瑞亚荆棘药水怎么做 荆棘药水能反弹多少伤害

泰拉瑞亚保暖药水怎么获得 保暖药水的合成方式分享

泰拉瑞亚保暖药水怎么获得 保暖药水的合成方式分享

泰拉瑞亚水上漂药水合成制作的方式分享

泰拉瑞亚水上漂药水合成制作的方式分享

泰拉瑞亚羽落药水怎么合成 羽落药水获取攻略分享

泰拉瑞亚羽落药水怎么合成 羽落药水获取攻略分享

泰拉瑞亚敏捷药水怎么做 敏捷药水合成制作详解

泰拉瑞亚敏捷药水怎么做 敏捷药水合成制作详解

泰拉瑞亚黑曜石皮药剂怎么合成 黑曜石皮药水怎么做

泰拉瑞亚黑曜石皮药剂怎么合成 黑曜石皮药水怎么做

泰拉瑞亚重力药水有什么用 重力药水怎么合成

泰拉瑞亚重力药水有什么用 重力药水怎么合成

泰拉瑞亚脚蹼药剂怎么获得 脚蹼药水合成方式分享

泰拉瑞亚脚蹼药剂怎么获得 脚蹼药水合成方式分享

水下神器 泰拉瑞亚鱼鳃药水怎么做 鱼鳃药剂合成方式攻略

水下神器 泰拉瑞亚鱼鳃药水怎么做 鱼鳃药剂合成方式攻略

泰拉瑞亚宝匣药水怎么做 宝匣药水合成配方和获取方法分享

泰拉瑞亚宝匣药水怎么做 宝匣药水合成配方和获取方法分享

泰拉瑞亚危险感药水怎么合成 危险感药水有什么用

泰拉瑞亚危险感药水怎么合成 危险感药水有什么用

泰拉瑞亚狩猎药水的合成方式分享 教你怎么获得狩猎药水

泰拉瑞亚狩猎药水的合成方式分享 教你怎么获得狩猎药水

泰拉瑞亚夜猫子药水怎么获得以及合成方式的分享

泰拉瑞亚夜猫子药水怎么获得以及合成方式的分享

泰拉瑞亚光芒药水有什么用 光芒药水怎么获得及合成方式

泰拉瑞亚光芒药水有什么用 光芒药水怎么获得及合成方式

泰拉瑞亚洞穴探险药水的作用和合成方式介绍

泰拉瑞亚洞穴探险药水的作用和合成方式介绍

泰拉瑞亚钓鱼药水怎么做 钓鱼药水合成表和获得方式分享

泰拉瑞亚钓鱼药水怎么做 钓鱼药水合成表和获得方式分享

泰拉瑞亚声纳药水合成方式方式 声纳药水有什么用

泰拉瑞亚声纳药水合成方式方式 声纳药水有什么用

泰拉瑞亚臭味药水有啥用 臭味药水合成方式分享

泰拉瑞亚臭味药水有啥用 臭味药水合成方式分享

泰拉瑞亚建筑工药水获得方法 让你快速建设家园

泰拉瑞亚建筑工药水获得方法 让你快速建设家园

泰拉瑞亚爱情药水有什么用 爱情药水怎么做呢

泰拉瑞亚爱情药水有什么用 爱情药水怎么做呢

泰拉瑞亚挖矿药水怎么合成 挖矿药水的作用和使用方法分享

泰拉瑞亚挖矿药水怎么合成 挖矿药水的作用和使用方法分享

泰拉瑞亚1.3.5全物品存档分享 小编亲测真实可用

泰拉瑞亚1.3.5全物品存档分享 小编亲测真实可用

泰拉瑞亚1.3.5.X通用版本极品射手存档分享 泰拉瑞亚角色存档下载

泰拉瑞亚1.3.5.X通用版本极品射手存档分享 泰拉瑞亚角色存档下载

泰拉瑞亚麦芽酒有什么用 教你麦芽酒怎么做

泰拉瑞亚麦芽酒有什么用 教你麦芽酒怎么做

泰拉瑞亚清酒有什么用 你知道清酒怎么做吗

泰拉瑞亚清酒有什么用 你知道清酒怎么做吗

泰拉瑞亚培根怎么做有什么用 泰拉瑞亚获取方式分享

泰拉瑞亚培根怎么做有什么用 泰拉瑞亚获取方式分享

泰拉瑞亚鱼菇汤有什么用 教你快速用烹饪锅合成鱼菇汤

泰拉瑞亚鱼菇汤有什么用 教你快速用烹饪锅合成鱼菇汤

泰拉瑞亚蜜糖饼干有什么用 蜜糖饼干制作方式分享

泰拉瑞亚蜜糖饼干有什么用 蜜糖饼干制作方式分享

泰拉瑞亚南瓜饼怎么做 南瓜饼的效果是什么

泰拉瑞亚南瓜饼怎么做 南瓜饼的效果是什么

泰拉瑞亚圣诞布丁有什么用 圣诞布丁怎么做

泰拉瑞亚圣诞布丁有什么用 圣诞布丁怎么做

泰拉瑞亚越南河粉怎么获得 越南河粉的合成方式分享

泰拉瑞亚越南河粉怎么获得 越南河粉的合成方式分享

泰拉瑞亚熟棉花糖有什么用 教你快速获取熟棉花糖

泰拉瑞亚熟棉花糖有什么用 教你快速获取熟棉花糖

泰拉瑞亚泰式炒面的作用合成方式分享

泰拉瑞亚泰式炒面的作用合成方式分享

泰拉瑞亚蛆虫汤有什么用 教你如何制作一锅蛆虫汤

泰拉瑞亚蛆虫汤有什么用 教你如何制作一锅蛆虫汤

泰拉瑞亚姜饼怎么获得 姜饼合成方式分享

泰拉瑞亚姜饼怎么获得 姜饼合成方式分享

泰拉瑞亚派对药剂有啥用 分享一下派对药剂怎么合成

泰拉瑞亚派对药剂有啥用 分享一下派对药剂怎么合成

泰拉瑞亚毒药药剂怎么获得 毒药药剂合成制作表

泰拉瑞亚毒药药剂怎么获得 毒药药剂合成制作表

泰拉瑞亚毒液药剂和毒药瓶有什么区别 毒液药剂怎么合成制作

泰拉瑞亚毒液药剂和毒药瓶有什么区别 毒液药剂怎么合成制作

泰拉瑞亚金药剂在哪里可以合成 金药剂合成之后有什么用

泰拉瑞亚金药剂在哪里可以合成 金药剂合成之后有什么用

泰拉瑞亚灵液药剂在哪合成 灵液药剂合成方式是什么分享

泰拉瑞亚灵液药剂在哪合成 灵液药剂合成方式是什么分享

泰拉瑞亚诅咒焰药剂有什么用 诅咒焰药剂怎么合成

泰拉瑞亚诅咒焰药剂有什么用 诅咒焰药剂怎么合成

泰拉瑞亚纳米机器人药剂是什么有什么用合成表

泰拉瑞亚纳米机器人药剂是什么有什么用合成表

泰拉瑞亚银矿怎么用 银矿在哪里哪里多

泰拉瑞亚银矿怎么用 银矿在哪里哪里多

泰拉瑞亚铁矿哪里多 应该在哪里挖铁矿

泰拉瑞亚铁矿哪里多 应该在哪里挖铁矿

泰拉瑞亚铅矿在哪里 铅矿怎么获得

泰拉瑞亚铅矿在哪里 铅矿怎么获得

泰拉瑞亚铜矿在哪里有什么用

泰拉瑞亚铜矿在哪里有什么用

泰拉瑞亚锡矿有什么用 锡矿石和铜矿石有什么区别吗

泰拉瑞亚锡矿有什么用 锡矿石和铜矿石有什么区别吗

泰拉瑞亚钨矿在哪怎么获得

泰拉瑞亚钨矿在哪怎么获得

泰拉瑞亚陨石坠落在哪里 陨石怎么挖

泰拉瑞亚陨石坠落在哪里 陨石怎么挖

泰拉瑞亚金矿在哪里有什么用 金矿和铂金矿有什么区别

泰拉瑞亚金矿在哪里有什么用 金矿和铂金矿有什么区别

泰拉瑞亚铂金矿在哪里怎么找到

泰拉瑞亚铂金矿在哪里怎么找到

泰拉瑞亚魔矿石有什么用 魔矿锭怎么获得怎么合成

泰拉瑞亚魔矿石有什么用 魔矿锭怎么获得怎么合成

泰拉瑞亚狱石怎么开采 狱岩石怎么挖怎么用

泰拉瑞亚狱石怎么开采 狱岩石怎么挖怎么用

泰拉瑞亚猩红矿石有什么用它在哪里

泰拉瑞亚猩红矿石有什么用它在哪里

泰拉瑞亚黑曜石怎么挖在哪里 怎么快速获得黑曜石

泰拉瑞亚黑曜石怎么挖在哪里 怎么快速获得黑曜石

泰拉瑞亚山铜矿怎么挖在哪里 山铜矿什么样图片分享

泰拉瑞亚山铜矿怎么挖在哪里 山铜矿什么样图片分享

泰拉瑞亚钴矿用什么挖在哪里找 寇伯特是什么东西

泰拉瑞亚钴矿用什么挖在哪里找 寇伯特是什么东西

泰拉瑞亚钯金矿在哪里怎么挖 钯金矿长什么样图片分享

泰拉瑞亚钯金矿在哪里怎么挖 钯金矿长什么样图片分享

泰拉瑞亚秘银矿长什么样怎么挖 秘银矿找不到怎么办

泰拉瑞亚秘银矿长什么样怎么挖 秘银矿找不到怎么办

泰拉瑞亚夜明矿有什么用 夜明矿在哪里怎么挖

泰拉瑞亚夜明矿有什么用 夜明矿在哪里怎么挖

泰拉瑞亚精金矿在哪里怎么挖 精金矿找不到怎么办

泰拉瑞亚精金矿在哪里怎么挖 精金矿找不到怎么办

泰拉瑞亚钛金矿在哪里怎么挖 钛金矿有什么用

泰拉瑞亚钛金矿在哪里怎么挖 钛金矿有什么用

泰拉瑞亚叶绿矿怎么挖 叶绿矿种植技巧分享

泰拉瑞亚叶绿矿怎么挖 叶绿矿种植技巧分享

泰拉瑞亚狱石锭怎么做有什么用 狱石锭合成表分享

泰拉瑞亚狱石锭怎么做有什么用 狱石锭合成表分享

泰拉瑞亚陨石锭有什么用怎么做 陨石锭合成表分享

泰拉瑞亚陨石锭有什么用怎么做 陨石锭合成表分享

泰拉瑞亚猩红矿锭有什么用可以做什么 猩红矿锭合成表分享

泰拉瑞亚猩红矿锭有什么用可以做什么 猩红矿锭合成表分享

泰拉瑞亚魔矿锭有什么用怎么获得 魔矿锭合成表分享

泰拉瑞亚魔矿锭有什么用怎么获得 魔矿锭合成表分享

泰拉瑞亚铂金锭有什么用怎么做 铂金锭合成表分享

泰拉瑞亚铂金锭有什么用怎么做 铂金锭合成表分享

泰拉瑞亚金锭怎么做有什么用 金锭合成表分享

泰拉瑞亚金锭怎么做有什么用 金锭合成表分享

泰拉瑞亚钨锭有什么用怎么做 钨锭合成表分享

泰拉瑞亚钨锭有什么用怎么做 钨锭合成表分享

泰拉瑞亚铅锭怎么合成有什么用 铅锭合成表分享

泰拉瑞亚铅锭怎么合成有什么用 铅锭合成表分享

泰拉瑞亚铁锭怎么做在哪挖 铁锭合成表分享

泰拉瑞亚铁锭怎么做在哪挖 铁锭合成表分享

泰拉瑞亚铜锭怎么得有什么用 铜锭合成表分享

泰拉瑞亚铜锭怎么得有什么用 铜锭合成表分享

泰拉瑞亚锡锭有什么用怎么做 锡锭合成表分享

泰拉瑞亚锡锭有什么用怎么做 锡锭合成表分享

泰拉瑞亚银锭怎么获得怎么做 银锭合成表分享

泰拉瑞亚银锭怎么获得怎么做 银锭合成表分享

泰拉瑞亚精金锭怎么合有什么用 精金锭合成方式分享

泰拉瑞亚精金锭怎么合有什么用 精金锭合成方式分享

泰拉瑞亚钴锭有什么用怎么获得 钴锭合成方式分享

泰拉瑞亚钴锭有什么用怎么获得 钴锭合成方式分享

泰拉瑞亚钯金锭怎么做怎么得 钯金锭合成方式分享

泰拉瑞亚钯金锭怎么做怎么得 钯金锭合成方式分享

泰拉瑞亚秘银锭怎么获得怎么挖 秘银锭合成表分享

泰拉瑞亚秘银锭怎么获得怎么挖 秘银锭合成表分享

泰拉瑞亚山铜锭怎么合成有什么用 山铜锭怎么合成山铜砧

泰拉瑞亚山铜锭怎么合成有什么用 山铜锭怎么合成山铜砧

泰拉瑞亚夜明锭怎么弄怎么获得 夜明锭合成表分享

泰拉瑞亚夜明锭怎么弄怎么获得 夜明锭合成表分享

泰拉瑞亚幽灵锭怎么获得有什么用 幽灵锭合成表分享

泰拉瑞亚幽灵锭怎么获得有什么用 幽灵锭合成表分享

泰拉瑞亚蘑菇矿锭怎么做有什么用 蘑菇矿锭合成表分享

泰拉瑞亚蘑菇矿锭怎么做有什么用 蘑菇矿锭合成表分享

泰拉瑞亚神圣锭怎么获得有什么用 神圣锭合成方式分享

泰拉瑞亚神圣锭怎么获得有什么用 神圣锭合成方式分享

泰拉瑞亚钛金锭怎么获得有什么用 钛金锭合成方式分享

泰拉瑞亚钛金锭怎么获得有什么用 钛金锭合成方式分享

泰拉瑞亚寒霜飞鱼是什么 寒霜飞鱼怎么获得有什么用

泰拉瑞亚寒霜飞鱼是什么 寒霜飞鱼怎么获得有什么用

泰拉瑞亚星形茴香怎么获得 八角茴香有什么用

泰拉瑞亚星形茴香怎么获得 八角茴香有什么用

泰拉瑞亚尖球有什么用 尖钉球陷阱怎么做

泰拉瑞亚尖球有什么用 尖钉球陷阱怎么做

泰拉瑞亚投刀怎么获得有什么用

泰拉瑞亚投刀怎么获得有什么用

泰拉瑞亚骨投刀怎么获得 骨制飞刀有什么用

泰拉瑞亚骨投刀怎么获得 骨制飞刀有什么用

泰拉瑞亚毒刀怎么解锁怎么获得 剧毒飞刀有什么用

泰拉瑞亚毒刀怎么解锁怎么获得 剧毒飞刀有什么用

泰拉瑞亚手里剑有什么用怎么获得 手里剑合成表分享

泰拉瑞亚手里剑有什么用怎么获得 手里剑合成表分享

泰拉瑞亚雪球怎么获得 雪球有什么用

泰拉瑞亚雪球怎么获得 雪球有什么用

泰拉瑞亚臭蛋有什么用能干嘛 用臭蛋可以杀死NPC吗

泰拉瑞亚臭蛋有什么用能干嘛 用臭蛋可以杀死NPC吗

泰拉瑞亚圣种怎么种植有是没用 圣种中不了怎么办

泰拉瑞亚圣种怎么种植有是没用 圣种中不了怎么办

泰拉瑞亚猩红种子有什么用怎么获得 猩红种子种植攻略

泰拉瑞亚猩红种子有什么用怎么获得 猩红种子种植攻略

泰拉瑞亚草种子怎么种植有什么用 草种子详细攻略

泰拉瑞亚草种子怎么种植有什么用 草种子详细攻略

泰拉瑞亚腐化种子怎么得到有是没用 腐化种子介绍

泰拉瑞亚腐化种子怎么得到有是没用 腐化种子介绍

泰拉瑞亚蘑菇草种子怎么获得怎么种植 蘑菇草种子种植介绍

泰拉瑞亚蘑菇草种子怎么获得怎么种植 蘑菇草种子种植介绍

泰拉瑞亚丛林草种子怎么种植有什么用 丛林草种子攻略分享

泰拉瑞亚丛林草种子怎么种植有什么用 丛林草种子攻略分享

泰拉瑞亚死亡草长在哪怎么种植 死亡草种子种植攻略

泰拉瑞亚死亡草长在哪怎么种植 死亡草种子种植攻略

泰拉瑞亚幌菊种子有什么用怎么获得 水叶草幌菊种植攻略

泰拉瑞亚幌菊种子有什么用怎么获得 水叶草幌菊种植攻略

泰拉瑞亚火焰花种子怎么获得有什么用 火焰花种植攻略

泰拉瑞亚火焰花种子怎么获得有什么用 火焰花种植攻略

泰拉瑞亚南瓜子怎么用种在哪 南瓜子种植攻略

泰拉瑞亚南瓜子怎么用种在哪 南瓜子种植攻略

泰拉瑞亚寒颤棘种子怎么获得怎么种植

泰拉瑞亚寒颤棘种子怎么获得怎么种植

泰拉瑞亚月光草种子怎么种植怎么获得

泰拉瑞亚月光草种子怎么种植怎么获得

泰拉瑞亚太阳花种子怎么种植怎么获得

泰拉瑞亚太阳花种子怎么种植怎么获得

泰拉瑞亚闪耀根种子怎么种植有什么用

泰拉瑞亚闪耀根种子怎么种植有什么用

泰拉瑞亚橡实怎么种植有什么用 橡果种植攻略分享

泰拉瑞亚橡实怎么种植有什么用 橡果种植攻略分享

泰拉瑞亚诅咒箭怎么做在哪里合成 诅咒箭的伤害是多少

泰拉瑞亚诅咒箭怎么做在哪里合成 诅咒箭的伤害是多少

泰拉瑞亚圣箭在哪里做配什么弓箭

泰拉瑞亚圣箭在哪里做配什么弓箭

泰拉瑞亚木箭怎么做能买吗 木箭在哪买攻略大全

泰拉瑞亚木箭怎么做能买吗 木箭在哪买攻略大全

泰拉瑞亚无尽箭袋有什么用怎么做 无尽箭袋合成配方分享

泰拉瑞亚无尽箭袋有什么用怎么做 无尽箭袋合成配方分享

泰拉瑞亚骨箭有什么用怎么获得

泰拉瑞亚骨箭有什么用怎么获得

泰拉瑞亚烈焰箭怎么做 召带火焰的箭怎么做

泰拉瑞亚烈焰箭怎么做 召带火焰的箭怎么做

泰拉瑞亚霜冻箭怎么做在哪里买 霜冻箭攻略分享

泰拉瑞亚霜冻箭怎么做在哪里买 霜冻箭攻略分享

泰拉瑞亚叶绿箭怎么做在哪里做 叶绿箭合成配方分享

泰拉瑞亚叶绿箭怎么做在哪里做 叶绿箭合成配方分享

泰拉瑞亚毒液箭怎么做 毒液箭和神圣箭哪个好

泰拉瑞亚毒液箭怎么做 毒液箭和神圣箭哪个好

泰拉瑞亚夜明箭怎么做 夜明箭厉害吗

泰拉瑞亚夜明箭怎么做 夜明箭厉害吗

泰拉瑞亚事件大全 泰拉瑞亚所有事件汇总表

泰拉瑞亚事件大全 泰拉瑞亚所有事件汇总表

泰拉瑞亚派对弹怎么做有什么用

泰拉瑞亚派对弹怎么做有什么用

泰拉瑞亚流星弹怎么做 流星弹找空岛怎么找

泰拉瑞亚流星弹怎么做 流星弹找空岛怎么找

泰拉瑞亚银子弹怎么做 银子弹在哪里购买

泰拉瑞亚银子弹怎么做 银子弹在哪里购买

泰拉瑞亚火枪子弹怎么做怎么获得 火枪子弹袋攻略

泰拉瑞亚火枪子弹怎么做怎么获得 火枪子弹袋攻略

泰拉瑞亚无尽火枪袋怎么做有什么用

泰拉瑞亚无尽火枪袋怎么做有什么用

泰拉瑞亚水晶子弹怎么做有什么用

泰拉瑞亚水晶子弹怎么做有什么用

泰拉瑞亚金子弹怎么做有什么用 金子弹合成表

泰拉瑞亚金子弹怎么做有什么用 金子弹合成表

泰拉瑞亚爆破弹怎么做有什么用 爆破弹厉害吗

泰拉瑞亚爆破弹怎么做有什么用 爆破弹厉害吗

泰拉瑞亚纳米弹有啥用怎么做 纳米弹攻略分享

泰拉瑞亚纳米弹有啥用怎么做 纳米弹攻略分享

泰拉瑞亚高射速子弹有什么用怎么做

泰拉瑞亚高射速子弹有什么用怎么做

泰拉瑞亚夜明弹可以追踪吗 夜明弹怎么做有什么用

泰拉瑞亚夜明弹可以追踪吗 夜明弹怎么做有什么用

泰拉瑞亚毒液弹怎么做有什么用 毒液弹攻略大全

泰拉瑞亚毒液弹怎么做有什么用 毒液弹攻略大全

泰拉瑞亚诅咒弹怎么做 诅咒弹作用是什么

泰拉瑞亚诅咒弹怎么做 诅咒弹作用是什么

泰拉瑞亚钉子怎么做怎么买 钉子有什么用

泰拉瑞亚钉子怎么做怎么买 钉子有什么用

泰拉瑞亚玉米糖子弹怎么获得有什么用

泰拉瑞亚玉米糖子弹怎么获得有什么用

泰拉瑞亚照明弹怎么做在哪里购买

泰拉瑞亚照明弹怎么做在哪里购买

泰拉瑞亚毒镖怎么用 毒镖用什么发射

泰拉瑞亚毒镖怎么用 毒镖用什么发射

泰拉瑞亚灵液镖是什么武器 灵液镖有什么用怎么做

泰拉瑞亚灵液镖是什么武器 灵液镖有什么用怎么做

泰拉瑞亚诅咒镖怎么用怎么获得

泰拉瑞亚诅咒镖怎么用怎么获得

泰拉瑞亚水晶镖怎么用怎么获得

泰拉瑞亚水晶镖怎么用怎么获得

泰拉瑞亚爆炸兔怎么用 爆炸兔怎么获得

泰拉瑞亚爆炸兔怎么用 爆炸兔怎么获得

泰拉瑞亚炮弹怎么得怎么用 炮弹攻略大全

泰拉瑞亚炮弹怎么得怎么用 炮弹攻略大全

泰拉瑞亚骨头怎么得有什么用 骨头攻略分享

泰拉瑞亚骨头怎么得有什么用 骨头攻略分享

泰拉瑞亚凝胶怎么刷 凝胶在哪里

泰拉瑞亚凝胶怎么刷 凝胶在哪里

泰拉瑞亚珊瑚怎么得 珊瑚有什么用

泰拉瑞亚珊瑚怎么得 珊瑚有什么用

泰拉瑞亚蛛网有什么用 蛛网怎么得

泰拉瑞亚蛛网有什么用 蛛网怎么得

泰拉瑞亚仙人掌可以种植吗 仙人掌有什么用

泰拉瑞亚仙人掌可以种植吗 仙人掌有什么用

泰拉瑞亚书有什么用 书怎么做

泰拉瑞亚书有什么用 书怎么做

泰拉瑞亚水晶碎块有什么用在哪里

泰拉瑞亚水晶碎块有什么用在哪里

泰拉瑞亚丛林孢子怎么获得有什么用

泰拉瑞亚丛林孢子怎么获得有什么用

泰拉瑞亚毒蘑菇怎么种怎么得 毒蘑菇详细攻略

泰拉瑞亚毒蘑菇怎么种怎么得 毒蘑菇详细攻略

泰拉瑞亚南瓜怎么种植怎么获得

泰拉瑞亚南瓜怎么种植怎么获得

泰拉瑞亚发光蘑菇怎么种植在哪里

泰拉瑞亚发光蘑菇怎么种植在哪里

泰拉瑞亚魔菇有什么用怎么获得

泰拉瑞亚魔菇有什么用怎么获得

泰拉瑞亚纳米机器人有什么用怎么获得

泰拉瑞亚纳米机器人有什么用怎么获得

泰拉瑞亚金尘有什么用怎么得

泰拉瑞亚金尘有什么用怎么得

泰拉瑞亚空滴管有什么用怎么获得 空滴管的作用分享

泰拉瑞亚空滴管有什么用怎么获得 空滴管的作用分享

泰拉瑞亚爆炸粉怎么得 爆炸粉攻略分享

泰拉瑞亚爆炸粉怎么得 爆炸粉攻略分享

泰拉瑞亚齿轮有什么用 齿轮墙如何获得

泰拉瑞亚齿轮有什么用 齿轮墙如何获得

泰拉瑞亚空心子弹合成表 空心子弹怎么用

泰拉瑞亚空心子弹合成表 空心子弹怎么用

泰拉瑞亚彩纸有什么用 彩纸怎么获得

泰拉瑞亚彩纸有什么用 彩纸怎么获得

泰拉瑞亚小瓶毒液怎么得 小瓶毒液有什么用

泰拉瑞亚小瓶毒液怎么得 小瓶毒液有什么用

泰拉瑞亚铃铛有什么用怎么得 铃铛合成方法

泰拉瑞亚铃铛有什么用怎么得 铃铛合成方法

泰拉瑞亚魔法书排行大全 魔法书怎么做

泰拉瑞亚魔法书排行大全 魔法书怎么做

泰拉瑞亚棉花糖怎么获得 棉花糖怎么烤

泰拉瑞亚棉花糖怎么获得 棉花糖怎么烤

泰拉瑞亚非法枪械部件有什么用什么时候买

泰拉瑞亚非法枪械部件有什么用什么时候买

泰拉瑞亚竖琴有什么用 竖琴合成方法分享

泰拉瑞亚竖琴有什么用 竖琴合成方法分享

泰拉瑞亚链条怎么得怎么合成

泰拉瑞亚链条怎么得怎么合成

泰拉瑞亚线有什么用 线怎么获得

泰拉瑞亚线有什么用 线怎么获得

泰拉瑞亚皮革怎么做 皮革有什么用

泰拉瑞亚皮革怎么做 皮革有什么用

泰拉瑞亚坚固头盔有什么用 坚固化石可以合成什么

泰拉瑞亚坚固头盔有什么用 坚固化石可以合成什么

泰拉饲养笼是干嘛的怎么使用 泰拉制笼机有什么用怎么放置

泰拉饲养笼是干嘛的怎么使用 泰拉制笼机有什么用怎么放置

泰拉瑞亚丝绸怎么做有什么用 丝绸合成表分享

泰拉瑞亚丝绸怎么做有什么用 丝绸合成表分享

泰拉瑞亚钻石有什么用 钻石怎么挖

泰拉瑞亚钻石有什么用 钻石怎么挖

泰拉瑞亚翡翠在哪里挖 翡翠钩怎么做

泰拉瑞亚翡翠在哪里挖 翡翠钩怎么做

泰拉瑞亚红玉在哪里怎么找 泰拉瑞亚红玉怎么快速获得

泰拉瑞亚红玉在哪里怎么找 泰拉瑞亚红玉怎么快速获得

泰拉瑞亚琥珀怎么得有什么用

泰拉瑞亚琥珀怎么得有什么用

泰拉瑞亚蓝玉有什么用 蓝玉怎么获得怎么弄

泰拉瑞亚蓝玉有什么用 蓝玉怎么获得怎么弄

泰拉瑞亚黄玉在哪挖怎么得 黄玉钩爪怎么制作

泰拉瑞亚黄玉在哪挖怎么得 黄玉钩爪怎么制作

泰拉瑞亚死亡草怎么快速获得 死亡草长在哪里

泰拉瑞亚死亡草怎么快速获得 死亡草长在哪里

泰拉瑞亚火焰花哪里有怎么种植

泰拉瑞亚火焰花哪里有怎么种植

泰拉瑞亚幌菊怎么开花 水叶草幌菊怎么种植

泰拉瑞亚幌菊怎么开花 水叶草幌菊怎么种植

泰拉瑞亚寒颤棘怎么种怎么开花

泰拉瑞亚寒颤棘怎么种怎么开花

泰拉瑞亚月光草怎么种 月光草哪里比较多

泰拉瑞亚月光草怎么种 月光草哪里比较多

泰拉瑞亚太阳花在哪里 太阳花怎么种

泰拉瑞亚太阳花在哪里 太阳花怎么种

泰拉瑞亚闪耀根怎么得怎么种 闪耀根种植攻略

泰拉瑞亚闪耀根怎么得怎么种 闪耀根种植攻略

泰拉瑞亚红外壳有什么用 红外壳怎么获得

泰拉瑞亚红外壳有什么用 红外壳怎么获得

泰拉瑞亚青外壳怎么获得 青外壳有什么用

泰拉瑞亚青外壳怎么获得 青外壳有什么用

泰拉瑞亚青绿蘑菇在哪里怎么获得

泰拉瑞亚青绿蘑菇在哪里怎么获得

泰拉瑞亚绿蘑菇在哪怎么得 绿蘑菇染料制作方法

泰拉瑞亚绿蘑菇在哪怎么得 绿蘑菇染料制作方法

泰拉瑞亚橙绿海藻有什么用怎么获得

泰拉瑞亚橙绿海藻有什么用怎么获得

泰拉瑞亚黄万寿菊怎么找有什么用

泰拉瑞亚黄万寿菊怎么找有什么用

泰拉瑞亚橙血根草有什么用在哪里

泰拉瑞亚橙血根草有什么用在哪里

泰拉瑞亚蓝浆果长什么样 蓝浆果在哪里

泰拉瑞亚蓝浆果长什么样 蓝浆果在哪里

泰拉瑞亚天蓝花朵在哪里有什么用

泰拉瑞亚天蓝花朵在哪里有什么用

泰拉瑞亚紫粘液有什么用 紫黏液怎么获得

泰拉瑞亚紫粘液有什么用 紫黏液怎么获得

泰拉瑞亚蓝紫外壳在哪有什么用

泰拉瑞亚蓝紫外壳在哪有什么用

泰拉瑞亚粉仙人掌果有什么用 粉仙人掌果怎么获得

泰拉瑞亚粉仙人掌果有什么用 粉仙人掌果怎么获得

泰拉瑞亚黑墨水有什么用怎么获得

泰拉瑞亚黑墨水有什么用怎么获得

泰拉瑞亚晶状体有什么用 晶状体怎么刷

泰拉瑞亚晶状体有什么用 晶状体怎么刷

泰拉瑞亚黑晶状体作用 黑晶状体怎么获得

泰拉瑞亚黑晶状体作用 黑晶状体怎么获得

泰拉瑞亚爪钩有什么用怎么做

泰拉瑞亚爪钩有什么用怎么做

泰拉瑞亚蜂蜡怎么获得有什么用 蜂蜡攻略分享

泰拉瑞亚蜂蜡怎么获得有什么用 蜂蜡攻略分享

泰拉瑞亚蚁狮上颚有什么用 蚁狮上颚合成表

泰拉瑞亚蚁狮上颚有什么用 蚁狮上颚合成表

泰拉瑞亚鲨鱼鳍怎么得到有啥用

泰拉瑞亚鲨鱼鳍怎么得到有啥用

泰拉瑞亚组织样本怎么获得有啥用

泰拉瑞亚组织样本怎么获得有啥用

泰拉瑞亚暗影鳞片怎么获得有什么用

泰拉瑞亚暗影鳞片怎么获得有什么用

泰拉瑞亚椎骨有什么用 椎骨合成不了怎么办

泰拉瑞亚椎骨有什么用 椎骨合成不了怎么办

泰拉瑞亚腐肉怎么获得有什么用

泰拉瑞亚腐肉怎么获得有什么用

泰拉瑞亚毒刺怎么获得 毒刺有什么用

泰拉瑞亚毒刺怎么获得 毒刺有什么用

泰拉瑞亚破布怎么获得有什么用 破布攻略分享

泰拉瑞亚破布怎么获得有什么用 破布攻略分享

泰拉瑞亚藤蔓怎么收集 藤蔓有什么用怎么获得

泰拉瑞亚藤蔓怎么收集 藤蔓有什么用怎么获得

泰拉瑞亚蠕虫毒牙有什么用怎么获得 蠕虫毒牙怎么打

泰拉瑞亚蠕虫毒牙有什么用怎么获得 蠕虫毒牙怎么打

泰拉瑞亚粉凝胶怎么获得有什么用

泰拉瑞亚粉凝胶怎么获得有什么用

泰拉瑞亚远古布匹有什么用 远古布匹怎么获得

泰拉瑞亚远古布匹有什么用 远古布匹怎么获得

泰拉瑞亚甲虫外壳可以做什么 甲虫外壳有什么用

泰拉瑞亚甲虫外壳可以做什么 甲虫外壳有什么用

泰拉瑞亚断裂英雄剑怎么获得有什么用

泰拉瑞亚断裂英雄剑怎么获得有什么用

泰拉瑞亚诅咒焰怎么获得 诅咒焰有什么用

泰拉瑞亚诅咒焰怎么获得 诅咒焰有什么用

泰拉瑞亚灵液有什么用 灵液在哪里得

泰拉瑞亚灵液有什么用 灵液在哪里得

泰拉瑞亚灵气怎么得有什么用 灵气合成表分享

泰拉瑞亚灵气怎么得有什么用 灵气合成表分享

泰拉瑞亚妖精尘有什么用 妖精尘怎么获得翅膀

泰拉瑞亚妖精尘有什么用 妖精尘怎么获得翅膀

泰拉瑞亚机械车轮片、机械车体片、机械电池片怎么获得怎么合成

泰拉瑞亚机械车轮片、机械车体片、机械电池片怎么获得怎么合成

泰拉瑞亚黑暗碎块有什么用 怎么获得

泰拉瑞亚黑暗碎块有什么用 怎么获得

泰拉瑞亚光明碎块有什么用 光明碎块怎么获得

泰拉瑞亚光明碎块有什么用 光明碎块怎么获得

泰拉瑞亚寒霜核有什么用怎么获得 寒霜核合成表攻略

泰拉瑞亚寒霜核有什么用怎么获得 寒霜核合成表攻略

泰拉瑞亚禁戒碎片有什么用可以干嘛

泰拉瑞亚禁戒碎片有什么用可以干嘛

泰拉瑞亚独角兽角有什么用怎么获得 独角兽角怎么刷攻略

泰拉瑞亚独角兽角有什么用怎么获得 独角兽角怎么刷攻略

泰拉瑞亚海龟壳怎么刷 海龟壳有什么用

泰拉瑞亚海龟壳怎么刷 海龟壳有什么用

泰拉瑞亚日耀碑牌碎片有什么用 日耀碑牌碎片怎么获得

泰拉瑞亚日耀碑牌碎片有什么用 日耀碑牌碎片怎么获得

泰拉瑞亚蜘蛛牙在哪怎么获得 蜘蛛牙合成表分享

泰拉瑞亚蜘蛛牙在哪怎么获得 蜘蛛牙合成表分享

泰拉瑞亚蝴蝶尘有什么用怎么获得

泰拉瑞亚蝴蝶尘有什么用怎么获得

泰拉瑞亚破蝙蝠之翼有什么用 蝙蝠之翼怎么合成

泰拉瑞亚破蝙蝠之翼有什么用 蝙蝠之翼怎么合成

泰拉瑞亚阴森嫩枝怎么获得 能干什么用

泰拉瑞亚阴森嫩枝怎么获得 能干什么用

泰拉瑞亚褴褛蜜蜂之翼有什么用 褴褛蜜蜂之翼怎么获得

泰拉瑞亚褴褛蜜蜂之翼有什么用 褴褛蜜蜂之翼怎么获得

泰拉瑞亚黑色仙尘有什么作用怎么获得 黑色仙尘翅膀好吗

泰拉瑞亚黑色仙尘有什么作用怎么获得 黑色仙尘翅膀好吗

泰拉瑞亚羽毛有什么用 羽毛怎么做翅膀

泰拉瑞亚羽毛有什么用 羽毛怎么做翅膀

泰拉瑞亚冰雪羽有什么用怎么得

泰拉瑞亚冰雪羽有什么用怎么得

泰拉瑞亚巨型鸟妖之羽怎么获得有什么用

泰拉瑞亚巨型鸟妖之羽怎么获得有什么用

泰拉瑞亚火羽怎么获得有什么用 火羽在哪里掉落

泰拉瑞亚火羽怎么获得有什么用 火羽在哪里掉落

泰拉瑞亚骨之羽怎么获得 骨之羽有什么用

泰拉瑞亚骨之羽怎么获得 骨之羽有什么用

泰拉瑞亚恐惧之魂有什么用怎么得 恐惧之魂合成表

泰拉瑞亚恐惧之魂有什么用怎么得 恐惧之魂合成表

泰拉瑞亚力量之魂怎么获得 力量之魂能合成什么

泰拉瑞亚力量之魂怎么获得 力量之魂能合成什么

泰拉瑞亚视域之魂在哪里能做什么

泰拉瑞亚视域之魂在哪里能做什么

泰拉瑞亚飞翔之魂有什么用在哪里获得

泰拉瑞亚飞翔之魂有什么用在哪里获得

泰拉瑞亚暗影之魂怎么获得有什么用

泰拉瑞亚暗影之魂怎么获得有什么用

泰拉瑞亚光明之魂怎么获得有什么用

泰拉瑞亚光明之魂怎么获得有什么用

泰拉瑞亚星尘碎片怎么获得有什么用 星尘碎片合成表分享

泰拉瑞亚星尘碎片怎么获得有什么用 星尘碎片合成表分享

泰拉瑞亚星云碎片怎么得有什么用

泰拉瑞亚星云碎片怎么得有什么用

泰拉瑞亚星旋碎片有什么用怎么获得 星旋碎片可以做啥

泰拉瑞亚星旋碎片有什么用怎么获得 星旋碎片可以做啥

泰拉瑞亚日耀碎片怎么获得有什么用

泰拉瑞亚日耀碎片怎么获得有什么用

泰拉瑞亚憎恶之蜂怎么用怎么合成 蜜蜂分泌物使用条件

泰拉瑞亚憎恶之蜂怎么用怎么合成 蜜蜂分泌物使用条件

泰拉瑞亚血腥脊椎怎么做有什么用

泰拉瑞亚血腥脊椎怎么做有什么用

泰拉瑞亚蠕虫诱饵怎么用怎么合成 蠕虫诱饵使用条件

泰拉瑞亚蠕虫诱饵怎么用怎么合成 蠕虫诱饵使用条件

泰拉瑞亚可疑眼球怎么召唤怎么合成

泰拉瑞亚可疑眼球怎么召唤怎么合成

泰拉瑞亚史莱姆王冠在哪合成怎么做

泰拉瑞亚史莱姆王冠在哪合成怎么做

泰拉瑞亚机械魔眼怎么合成怎么召唤

泰拉瑞亚机械魔眼怎么合成怎么召唤

泰拉瑞亚机械蠕虫合成方法 机械蠕虫怎么召唤使用

泰拉瑞亚机械蠕虫合成方法 机械蠕虫怎么召唤使用

泰拉瑞亚机械骷髅头怎么做怎么用

泰拉瑞亚机械骷髅头怎么做怎么用

泰拉瑞亚天界符怎么用 天界符使用条件合成方式分享

泰拉瑞亚天界符怎么用 天界符使用条件合成方式分享

泰拉瑞亚丛林蜥蜴电池有什么用怎么用

泰拉瑞亚丛林蜥蜴电池有什么用怎么用

泰拉瑞亚哥布林战旗怎么做怎么召唤

泰拉瑞亚哥布林战旗怎么做怎么召唤

泰拉瑞亚日耀碑牌什么时候用 日耀碑牌怎么用

泰拉瑞亚日耀碑牌什么时候用 日耀碑牌怎么用

泰拉瑞亚调皮礼物怎么用怎么获得 调皮礼物掉落分享

泰拉瑞亚调皮礼物怎么用怎么获得 调皮礼物掉落分享

泰拉瑞亚南瓜月勋章怎么做 南瓜月勋章怎么合成

泰拉瑞亚南瓜月勋章怎么做 南瓜月勋章怎么合成

泰拉瑞亚水晶雪球怎么获得怎么做 水晶雪球有什么用

泰拉瑞亚水晶雪球怎么获得怎么做 水晶雪球有什么用

泰拉瑞亚永恒水晶攻略介绍

泰拉瑞亚永恒水晶攻略介绍

泰拉瑞亚光明钥匙有什么用怎么获得 光明钥匙怎么做

泰拉瑞亚光明钥匙有什么用怎么获得 光明钥匙怎么做

泰拉瑞亚夜光钥匙有什么用怎么用 夜光钥匙获得攻略

泰拉瑞亚夜光钥匙有什么用怎么用 夜光钥匙获得攻略

泰拉瑞亚神庙钥匙怎么得到怎么使用 神庙钥匙合成方式

泰拉瑞亚神庙钥匙怎么得到怎么使用 神庙钥匙合成方式

泰拉瑞亚金钥匙怎么获得有什么用

泰拉瑞亚金钥匙怎么获得有什么用

泰拉瑞亚暗影钥匙怎么获得有什么用

泰拉瑞亚暗影钥匙怎么获得有什么用

泰拉瑞亚金锁盒是什么 金锁盒怎么获得

泰拉瑞亚金锁盒是什么 金锁盒怎么获得

泰拉瑞亚礼袋能开什么 礼袋有什么用怎么获得

泰拉瑞亚礼袋能开什么 礼袋有什么用怎么获得

泰拉瑞亚草药袋怎么获得怎么弄 草药袋打不开怎么办

泰拉瑞亚草药袋怎么获得怎么弄 草药袋打不开怎么办

泰拉瑞亚礼物怎么得到怎么打开

泰拉瑞亚礼物怎么得到怎么打开

泰拉瑞亚宝藏袋怎么获得有什么用 宝藏袋怎么打开

泰拉瑞亚宝藏袋怎么获得有什么用 宝藏袋怎么打开

泰拉瑞亚护卫奖章怎么获得 护卫奖章有什么用

泰拉瑞亚护卫奖章怎么获得 护卫奖章有什么用

泰拉瑞亚荧光棒怎么做 荧光棒制作攻略

泰拉瑞亚荧光棒怎么做 荧光棒制作攻略

泰拉瑞亚彩纸枪怎么获得有什么用

泰拉瑞亚彩纸枪怎么获得有什么用

泰拉瑞亚烟雾弹有什么用

泰拉瑞亚烟雾弹有什么用

泰拉瑞亚森林生物群落详细介绍

泰拉瑞亚森林生物群落详细介绍

泰拉瑞亚地表蘑菇生物群落怎么生成

泰拉瑞亚地表蘑菇生物群落怎么生成

泰拉瑞亚海洋生物群落攻略 海洋生物群系有些什么怪

泰拉瑞亚海洋生物群落攻略 海洋生物群系有些什么怪

泰拉瑞亚地牢生物群落介绍与攻略

泰拉瑞亚地牢生物群落介绍与攻略

泰拉瑞亚沙漠生物群落介绍攻略

泰拉瑞亚沙漠生物群落介绍攻略

泰拉瑞亚丛林生物群落介绍 如何建立新的丛林

泰拉瑞亚丛林生物群落介绍 如何建立新的丛林

泰拉瑞亚雪原生物群落介绍与攻略

泰拉瑞亚雪原生物群落介绍与攻略

泰拉瑞亚太空生物群落介绍与攻略

泰拉瑞亚太空生物群落介绍与攻略

泰拉瑞亚神圣之地在哪里 神圣之地生物群落介绍与攻略

泰拉瑞亚神圣之地在哪里 神圣之地生物群落介绍与攻略

泰拉瑞亚地下生物群落介绍与攻略

泰拉瑞亚地下生物群落介绍与攻略

泰拉瑞亚地下雪原介绍 地下苔原生物群落攻略

泰拉瑞亚地下雪原介绍 地下苔原生物群落攻略

泰拉瑞亚地下沙漠生物群落介绍与攻略

泰拉瑞亚地下沙漠生物群落介绍与攻略

泰拉瑞亚地下丛林生物群落介绍 地下森林在哪里

泰拉瑞亚地下丛林生物群落介绍 地下森林在哪里

泰拉瑞亚地狱生物群落 泰拉瑞亚地狱怎么去

泰拉瑞亚地狱生物群落 泰拉瑞亚地狱怎么去

泰拉瑞亚蜘蛛巢生物群落介绍 蜘蛛巢怎么找

泰拉瑞亚蜘蛛巢生物群落介绍 蜘蛛巢怎么找

泰拉瑞亚大理石洞生物群落介绍与攻略

泰拉瑞亚大理石洞生物群落介绍与攻略

泰拉瑞亚丛林神庙生物群落介绍 丛林神庙怎么进去

泰拉瑞亚丛林神庙生物群落介绍 丛林神庙怎么进去

泰拉瑞亚蜂巢怎么找 蜂巢生物群落介绍与攻略

泰拉瑞亚蜂巢怎么找 蜂巢生物群落介绍与攻略

泰拉瑞亚花岗岩洞生物群落介绍与攻略

泰拉瑞亚花岗岩洞生物群落介绍与攻略

泰拉瑞亚金字塔在哪里怎么找 金字塔生物群落介绍

泰拉瑞亚金字塔在哪里怎么找 金字塔生物群落介绍

泰拉瑞亚生命树有什么用 生命树下面有什么

泰拉瑞亚生命树有什么用 生命树下面有什么

泰拉瑞亚浮空岛怎么找 漂浮岛在哪里有几个

泰拉瑞亚浮空岛怎么找 漂浮岛在哪里有几个

泰拉瑞亚附魔剑冢怎么找 附魔剑冢在哪里

泰拉瑞亚附魔剑冢怎么找 附魔剑冢在哪里

泰拉瑞亚铜短剑介绍 铜短剑怎么获得

泰拉瑞亚铜短剑介绍 铜短剑怎么获得

泰拉瑞亚锡短剑怎么制作 锡短剑介绍攻略

泰拉瑞亚锡短剑怎么制作 锡短剑介绍攻略

泰拉瑞亚木剑怎么做 木剑介绍与攻略

泰拉瑞亚木剑怎么做 木剑介绍与攻略

泰拉瑞亚铜阔剑要用什么来做 铜阔剑怎么做

泰拉瑞亚铜阔剑要用什么来做 铜阔剑怎么做

泰拉瑞亚针叶木剑怎么做 针叶木剑介绍

泰拉瑞亚针叶木剑怎么做 针叶木剑介绍

泰拉瑞亚铁短剑怎么做 铁短剑介绍攻略

泰拉瑞亚铁短剑怎么做 铁短剑介绍攻略

泰拉瑞亚棕榈木剑怎么做怎么获得 棕榈木剑介绍攻略

泰拉瑞亚棕榈木剑怎么做怎么获得 棕榈木剑介绍攻略

泰拉瑞亚红木剑怎么做怎么获得 红木剑ID与介绍

泰拉瑞亚红木剑怎么做怎么获得 红木剑ID与介绍

泰拉瑞亚仙人掌剑怎么做 仙人掌剑伤害高吗

泰拉瑞亚仙人掌剑怎么做 仙人掌剑伤害高吗

泰拉瑞亚铅短剑怎么获得 铅质短剑id介绍与攻略

泰拉瑞亚铅短剑怎么获得 铅质短剑id介绍与攻略

泰拉瑞亚银短剑怎么做怎么获得 银短剑介绍与攻略

泰拉瑞亚银短剑怎么做怎么获得 银短剑介绍与攻略

泰拉瑞亚锡宽剑怎么制作 锡宽剑ID与属性介绍

泰拉瑞亚锡宽剑怎么制作 锡宽剑ID与属性介绍

泰拉瑞亚铁阔剑怎么合成 铁阔剑ID与属性介绍

泰拉瑞亚铁阔剑怎么合成 铁阔剑ID与属性介绍

泰拉瑞亚乌木剑怎么做 乌木剑属性介绍攻略

泰拉瑞亚乌木剑怎么做 乌木剑属性介绍攻略

泰拉瑞亚暗影木剑怎么制作 暗影木剑id与属性攻略

泰拉瑞亚暗影木剑怎么制作 暗影木剑id与属性攻略

泰拉瑞亚钨短剑怎么做 钨短剑ID与属性介绍

泰拉瑞亚钨短剑怎么做 钨短剑ID与属性介绍

泰拉瑞亚银阔剑最高品质的附魔是什么 银阔剑怎么做

泰拉瑞亚银阔剑最高品质的附魔是什么 银阔剑怎么做

泰拉瑞亚铅宽剑怎么做 铅宽剑id与属性介绍

泰拉瑞亚铅宽剑怎么做 铅宽剑id与属性介绍

泰拉瑞亚金短剑怎么做 金短剑id与属性介绍

泰拉瑞亚金短剑怎么做 金短剑id与属性介绍

泰拉瑞亚利刃手套合成方式 利刃手套怎么获得

泰拉瑞亚利刃手套合成方式 利刃手套怎么获得

泰拉瑞亚颌骨剑怎么做 颌骨剑厉害吗

泰拉瑞亚颌骨剑怎么做 颌骨剑厉害吗

泰拉瑞亚铂金短剑怎么获得 铂金短剑id与属性介绍

泰拉瑞亚铂金短剑怎么获得 铂金短剑id与属性介绍

泰拉瑞亚金阔剑属性最好是什么 金阔剑怎么做

泰拉瑞亚金阔剑属性最好是什么 金阔剑怎么做

泰拉瑞亚僵尸臂是什么 僵尸手臂有什么用怎么获得

泰拉瑞亚僵尸臂是什么 僵尸手臂有什么用怎么获得

泰拉瑞亚钨宽剑怎么获得 钨制宽剑id与属性介绍

泰拉瑞亚钨宽剑怎么获得 钨制宽剑id与属性介绍

泰拉瑞亚时尚剪刀是什么怎么得 时尚剪刀武器攻略

泰拉瑞亚时尚剪刀是什么怎么得 时尚剪刀武器攻略

泰拉瑞亚铂金宽剑和短剑有什么区别 铂金宽剑怎么获得

泰拉瑞亚铂金宽剑和短剑有什么区别 铂金宽剑怎么获得

泰拉瑞亚武士刀能合成吗 武士刀好用吗怎么获得

泰拉瑞亚武士刀能合成吗 武士刀好用吗怎么获得

泰拉瑞亚糖棒剑id与属性介绍 棒棒糖剑怎么获得

泰拉瑞亚糖棒剑id与属性介绍 棒棒糖剑怎么获得

泰拉瑞亚骨剑有什么用 骨剑怎么获得

泰拉瑞亚骨剑有什么用 骨剑怎么获得

泰拉瑞亚村正大刀合成方法分享 村正大刀有什么用厉害吗

泰拉瑞亚村正大刀合成方法分享 村正大刀有什么用厉害吗

泰拉瑞亚陨石光剑能合成什么 陨石光剑好用吗

泰拉瑞亚陨石光剑能合成什么 陨石光剑好用吗

泰拉瑞亚异域弯刀怎么获得 外星弯刀介绍与攻略

泰拉瑞亚异域弯刀怎么获得 外星弯刀介绍与攻略

泰拉瑞亚猎鹰刃怎么得到 猎鹰刃好用不好用

泰拉瑞亚猎鹰刃怎么得到 猎鹰刃好用不好用

泰拉瑞亚炽焰巨剑(火山)怎么做有什么用 炽焰巨剑可以合成什么

泰拉瑞亚炽焰巨剑(火山)怎么做有什么用 炽焰巨剑可以合成什么

泰拉瑞亚紫挥棒鱼介绍与攻略 紫色棒鱼怎么做

泰拉瑞亚紫挥棒鱼介绍与攻略 紫色棒鱼怎么做

泰拉瑞亚星怒怎么升级 星怒剑怎么获得

泰拉瑞亚星怒怎么升级 星怒剑怎么获得

泰拉瑞亚血腥屠刀可以合成什么 血腥屠刀怎么做

泰拉瑞亚血腥屠刀可以合成什么 血腥屠刀怎么做

泰拉瑞亚钴剑怎么做 钴剑id与属性介绍

泰拉瑞亚钴剑怎么做 钴剑id与属性介绍

泰拉瑞亚毁灭刃在哪里能干嘛 毁灭刃可以合成吗

泰拉瑞亚毁灭刃在哪里能干嘛 毁灭刃可以合成吗

泰拉瑞亚拍拍手是什么怎么得 拍拍手武器获得方式

泰拉瑞亚拍拍手是什么怎么得 拍拍手武器获得方式

泰拉瑞亚精致手杖怎么获得 优雅手杖介绍与攻略

泰拉瑞亚精致手杖怎么获得 优雅手杖介绍与攻略

泰拉瑞亚珍珠木剑怎么获得 珍珠木剑id与属性介绍

泰拉瑞亚珍珠木剑怎么获得 珍珠木剑id与属性介绍

泰拉瑞亚钯金剑好吗最高品质是什么 钯金剑详细攻略

泰拉瑞亚钯金剑好吗最高品质是什么 钯金剑详细攻略

泰拉瑞亚冰雪镰刀怎么获得 冰雪镰刀最高属性是什么

泰拉瑞亚冰雪镰刀怎么获得 冰雪镰刀最高属性是什么

泰拉瑞亚地狱烙印怎么格挡右键怎么使用 地狱烙印介绍攻略

泰拉瑞亚地狱烙印怎么格挡右键怎么使用 地狱烙印介绍攻略

泰拉瑞亚晶光刃怎么获得怎么制作 晶光刃合成方式分享

泰拉瑞亚晶光刃怎么获得怎么制作 晶光刃合成方式分享

泰拉瑞亚秘银剑详细攻略 秘银重剑怎么样

泰拉瑞亚秘银剑详细攻略 秘银重剑怎么样

泰拉瑞亚山铜剑怎么制作 山铜剑好吗

泰拉瑞亚山铜剑怎么制作 山铜剑好吗

泰拉瑞亚精金剑可以合成什么 精金剑伤害高吗怎么制作

泰拉瑞亚精金剑可以合成什么 精金剑伤害高吗怎么制作

泰拉瑞亚霜印剑好用吗 霜印剑怎么获得

泰拉瑞亚霜印剑好用吗 霜印剑怎么获得

泰拉瑞亚短弯刀附魔最强是什么 短弯刀和海盗弯刀区别

泰拉瑞亚短弯刀附魔最强是什么 短弯刀和海盗弯刀区别

泰拉瑞亚叶绿军刀怎么做 叶绿军刀和双刃剑有什么区别

泰拉瑞亚叶绿军刀怎么做 叶绿军刀和双刃剑有什么区别

泰拉瑞亚光束剑怎么获得 光束剑可以合成什么

泰拉瑞亚光束剑怎么获得 光束剑可以合成什么

泰拉瑞亚钛金剑附魔最好的前缀是什么 钛金剑伤害介绍

泰拉瑞亚钛金剑附魔最好的前缀是什么 钛金剑伤害介绍

泰拉瑞亚舌锋剑有什么用 舌锋剑怎么做

泰拉瑞亚舌锋剑有什么用 舌锋剑怎么做

泰拉瑞亚死神镰刀爆率多少怎么获得 死神镰刀最好附魔

泰拉瑞亚死神镰刀爆率多少怎么获得 死神镰刀最好附魔

泰拉瑞亚断钢剑怎么做在哪里 断钢剑有什么用

泰拉瑞亚断钢剑怎么做在哪里 断钢剑有什么用

泰拉瑞亚种子弯刀好吗 种子弯刀怎么得到

泰拉瑞亚种子弯刀好吗 种子弯刀怎么得到

泰拉瑞亚叶绿双刃刀详解 叶绿双刃剑武器详细攻略

泰拉瑞亚叶绿双刃刀详解 叶绿双刃剑武器详细攻略

泰拉瑞亚钥匙剑强不强有什么用 钥匙剑怎么获得

泰拉瑞亚钥匙剑强不强有什么用 钥匙剑怎么获得

泰拉瑞亚臭虎爪附魔搭配 臭虎爪如何dps3000

泰拉瑞亚臭虎爪附魔搭配 臭虎爪如何dps3000

泰拉瑞亚木悠悠球可以做什么 木悠悠球合成怎么做

泰拉瑞亚木悠悠球可以做什么 木悠悠球合成怎么做

泰拉瑞亚对打球怎么得有什么用

泰拉瑞亚对打球怎么得有什么用

泰拉瑞亚抑郁球好吗 抑郁球可以用什么造

泰拉瑞亚抑郁球好吗 抑郁球可以用什么造

泰拉瑞亚血脉球厉害吗 血脉球怎么做怎么获得

泰拉瑞亚血脉球厉害吗 血脉球怎么做怎么获得

泰拉瑞亚亚马逊球附魔最好是什么 亚马逊球怎么做

泰拉瑞亚亚马逊球附魔最好是什么 亚马逊球怎么做

泰拉瑞亚克苏鲁之眼悠悠球怎么得怎么合成

泰拉瑞亚克苏鲁之眼悠悠球怎么得怎么合成

泰拉瑞亚喷流球怎么做 喷流球最高品质是什么

泰拉瑞亚喷流球怎么做 喷流球最高品质是什么

泰拉瑞亚英勇球稀有吗 英勇球id与属性介绍

泰拉瑞亚英勇球稀有吗 英勇球id与属性介绍

泰拉瑞亚初号机悠悠球怎么得 代码1球详细攻略

泰拉瑞亚初号机悠悠球怎么得 代码1球详细攻略

泰拉瑞亚好胜球怎么获得 好胜球有用吗

泰拉瑞亚好胜球怎么获得 好胜球有用吗

泰拉瑞亚渐变球好用吗 渐变球怎么获得

泰拉瑞亚渐变球好用吗 渐变球怎么获得

泰拉瑞亚吉克球制作方式是什么 吉克球怎么获得

泰拉瑞亚吉克球制作方式是什么 吉克球怎么获得

泰拉瑞亚狱火球怎么得 狱火球最高等级附魔是什么

泰拉瑞亚狱火球怎么得 狱火球最高等级附魔是什么

泰拉瑞亚冰雪悠悠球掉落几率 冰雪悠悠球最好的附魔

泰拉瑞亚冰雪悠悠球掉落几率 冰雪悠悠球最好的附魔

泰拉瑞亚叶列茨球附魔最好是什么 叶列茨球详细攻略wiki

泰拉瑞亚叶列茨球附魔最好是什么 叶列茨球详细攻略wiki

泰拉瑞亚代码2球怎么获得 code2悠悠球获得方式

泰拉瑞亚代码2球怎么获得 code2悠悠球获得方式

泰拉瑞亚女武神悠悠球如何获得怎么合成 女武神悠悠球攻略

泰拉瑞亚女武神悠悠球如何获得怎么合成 女武神悠悠球攻略

泰拉瑞亚Red的抛球怎么获得 Red的抛球id详细介绍

泰拉瑞亚Red的抛球怎么获得 Red的抛球id详细介绍

泰拉瑞亚克拉肯球最好的附魔 克拉肯球属性介绍

泰拉瑞亚克拉肯球最好的附魔 克拉肯球属性介绍

泰拉瑞亚长矛合成表 长矛怎么制作有什么用

泰拉瑞亚长矛合成表 长矛怎么制作有什么用

泰拉瑞亚三叉戟怎么得 三叉戟有什么用

泰拉瑞亚三叉戟怎么得 三叉戟有什么用

泰拉瑞亚腐叉有什么用 腐叉介绍与攻略

泰拉瑞亚腐叉有什么用 腐叉介绍与攻略

泰拉瑞亚剑鱼有什么用 剑鱼在哪里钓怎么获得

泰拉瑞亚剑鱼有什么用 剑鱼在哪里钓怎么获得

泰拉瑞亚暗黑长戟怎么获得 暗黑长枪详细攻略

泰拉瑞亚暗黑长戟怎么获得 暗黑长枪详细攻略

泰拉瑞亚钴剃刀怎么样 钴薙刀介绍与详细攻略

泰拉瑞亚钴剃刀怎么样 钴薙刀介绍与详细攻略

泰拉瑞亚精金关刀怎么获得 精金长刀id与属性介绍

泰拉瑞亚精金关刀怎么获得 精金长刀id与属性介绍

泰拉瑞亚山铜长戟怎么获得 山铜长戟介绍与攻略

泰拉瑞亚山铜长戟怎么获得 山铜长戟介绍与攻略

泰拉瑞亚秘银长戟有穿透效果吗 秘银长戟介绍与攻略

泰拉瑞亚秘银长戟有穿透效果吗 秘银长戟介绍与攻略

泰拉瑞亚钯金刺矛厉害吗 钯金刺矛详细介绍

泰拉瑞亚钯金刺矛厉害吗 钯金刺矛详细介绍

泰拉瑞亚蜻蛉切怎么做怎么合成 蜻蛉切详细攻略

泰拉瑞亚蜻蛉切怎么做怎么合成 蜻蛉切详细攻略

泰拉瑞亚叶绿镋怎么做怎么获得 叶绿镋详细攻略

泰拉瑞亚叶绿镋怎么做怎么获得 叶绿镋详细攻略

泰拉瑞亚恐怖关刀怎么得 恐怖关刀附魔最好是什么

泰拉瑞亚恐怖关刀怎么得 恐怖关刀附魔最好是什么

泰拉瑞亚永恒之枪合成有什么用 永恒之枪能合成什么武器

泰拉瑞亚永恒之枪合成有什么用 永恒之枪能合成什么武器

泰拉瑞亚钛金三叉戟怎么获得 钛金三叉戟介绍与攻略

泰拉瑞亚钛金三叉戟怎么获得 钛金三叉戟介绍与攻略

泰拉瑞亚北极怎么获得 北极矛最高附魔介绍

泰拉瑞亚北极怎么获得 北极矛最高附魔介绍

泰拉瑞亚黑曜石剑鱼怎么获得怎么做 黑曜石剑鱼最好附魔

泰拉瑞亚黑曜石剑鱼怎么获得怎么做 黑曜石剑鱼最好附魔

泰拉瑞亚蘑菇长矛最高附魔是什么 蘑菇长矛怎么获得介绍

泰拉瑞亚蘑菇长矛最高附魔是什么 蘑菇长矛怎么获得介绍

泰拉瑞亚木制回旋镖怎么制作 木制回旋镖详细攻略

泰拉瑞亚木制回旋镖怎么制作 木制回旋镖详细攻略

泰拉瑞亚附魔回旋镖可以合成什么 附魔回旋镖在哪有什么用

泰拉瑞亚附魔回旋镖可以合成什么 附魔回旋镖在哪有什么用

泰拉瑞亚水果蛋糕旋刃有什么用怎么获得

泰拉瑞亚水果蛋糕旋刃有什么用怎么获得

泰拉瑞亚血腥砍刀怎么获得 血腥砍刀有什么用

泰拉瑞亚血腥砍刀怎么获得 血腥砍刀有什么用

泰拉瑞亚冰雪回旋镖怎么获得有什么用 冰雪回旋镖附魔最好是什么

泰拉瑞亚冰雪回旋镖怎么获得有什么用 冰雪回旋镖附魔最好是什么

泰拉瑞亚荆棘旋刃附魔 荆棘旋刃能否叠加说明

泰拉瑞亚荆棘旋刃附魔 荆棘旋刃能否叠加说明

泰拉瑞亚烈焰回旋镖怎么获得怎么做

泰拉瑞亚烈焰回旋镖怎么获得怎么做

泰拉瑞亚飞刀怎么得 飞刀id与属性详细介绍

泰拉瑞亚飞刀怎么得 飞刀id与属性详细介绍

泰拉瑞亚光辉飞盘怎么附魔怎么获得 光辉飞盘有什么用

泰拉瑞亚光辉飞盘怎么附魔怎么获得 光辉飞盘有什么用

泰拉瑞亚疯狂飞斧最好附魔前缀 疯狂飞斧详细介绍

泰拉瑞亚疯狂飞斧最好附魔前缀 疯狂飞斧详细介绍

泰拉瑞亚圣骑士锤掉率爆率高吗 圣骑士锤最高附魔

泰拉瑞亚圣骑士锤掉率爆率高吗 圣骑士锤最高附魔

泰拉瑞亚链刀怎么做怎么得 链刀有多少种

泰拉瑞亚链刀怎么做怎么得 链刀有多少种

泰拉瑞亚链球最好附魔 链球怎么做

泰拉瑞亚链球最好附魔 链球怎么做

泰拉瑞亚血肉之球有什么用 血肉之球用法以及掉落

泰拉瑞亚血肉之球有什么用 血肉之球用法以及掉落

泰拉瑞亚蓝月能合成什么有什么用 蓝月连枷详细攻略

泰拉瑞亚蓝月能合成什么有什么用 蓝月连枷详细攻略

泰拉瑞亚阳炎之怒怎么用 阳炎之怒最高附魔是什么

泰拉瑞亚阳炎之怒怎么用 阳炎之怒最高附魔是什么

泰拉瑞亚锚怎么获得 锚详细介绍

泰拉瑞亚锚怎么获得 锚详细介绍

泰拉瑞亚致胜炮怎么样 致胜炮属性最好附魔是什么

泰拉瑞亚致胜炮怎么样 致胜炮属性最好附魔是什么

泰拉瑞亚铁链血滴子附魔最好是什么 铁链血滴子详细介绍

泰拉瑞亚铁链血滴子附魔最好是什么 铁链血滴子详细介绍

泰拉瑞亚太极连枷怎么做怎么用 太极连枷好用吗

泰拉瑞亚太极连枷怎么做怎么用 太极连枷好用吗

泰拉瑞亚花冠怎么获得 花冠有用吗详细介绍

泰拉瑞亚花冠怎么获得 花冠有用吗详细介绍

泰拉瑞亚猪鲨链球最好附魔 猪鲨链球前缀属性最好是什么

泰拉瑞亚猪鲨链球最好附魔 猪鲨链球前缀属性最好是什么

泰拉瑞亚石巨人之拳附魔最好是什么 石巨人之拳好用吗

泰拉瑞亚石巨人之拳附魔最好是什么 石巨人之拳好用吗

泰拉瑞亚暗影焰刀怎么得 暗影焰刀前缀最好是什么

泰拉瑞亚暗影焰刀怎么得 暗影焰刀前缀最好是什么

泰拉瑞亚瞌睡章鱼怎么获得 瞌睡章鱼补充能量介绍

泰拉瑞亚瞌睡章鱼怎么获得 瞌睡章鱼补充能量介绍

泰拉瑞亚腐化者之戟附魔 腐化者之戟怎么得

泰拉瑞亚腐化者之戟附魔 腐化者之戟怎么得

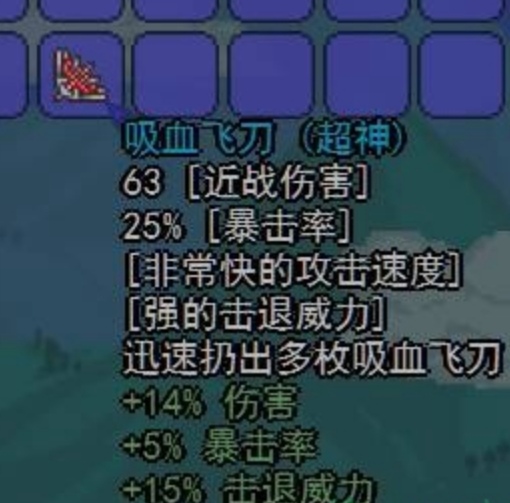

泰拉瑞亚吸血鬼刀最高附魔是什么 吸血鬼刀怎么获得

泰拉瑞亚吸血鬼刀最高附魔是什么 吸血鬼刀怎么获得

泰拉瑞亚木弓怎么做怎么获得 木弓介绍攻略

泰拉瑞亚木弓怎么做怎么获得 木弓介绍攻略

泰拉瑞亚针叶木弓怎么获得 针叶木弓附魔介绍

泰拉瑞亚针叶木弓怎么获得 针叶木弓附魔介绍

泰拉瑞亚黄铜弓怎么制作怎么合成 铜弓id介绍

泰拉瑞亚黄铜弓怎么制作怎么合成 铜弓id介绍

泰拉瑞亚棕榈木弓怎么获得 棕榈木弓id与属性介绍

泰拉瑞亚棕榈木弓怎么获得 棕榈木弓id与属性介绍

泰拉瑞亚红木弓怎么获得怎么制作

泰拉瑞亚红木弓怎么获得怎么制作

泰拉瑞亚锡弓怎么获得 锡弓id与属性怎么样

泰拉瑞亚锡弓怎么获得 锡弓id与属性怎么样

泰拉瑞亚乌木弓怎么获得厉害吗 乌木弓id与属性介绍

泰拉瑞亚乌木弓怎么获得厉害吗 乌木弓id与属性介绍

泰拉瑞亚铁弓箭怎么做 铁弓怎么获得以及属性介绍

泰拉瑞亚铁弓箭怎么做 铁弓怎么获得以及属性介绍

泰拉瑞亚暗影木弓怎么获得 暗影木弓id与属性详细介绍

泰拉瑞亚暗影木弓怎么获得 暗影木弓id与属性详细介绍

泰拉瑞亚铅弓怎么获得厉害吗 铅弓id与属性介绍

泰拉瑞亚铅弓怎么获得厉害吗 铅弓id与属性介绍

泰拉瑞亚银弓最好属性 银弓最高品质是什么

泰拉瑞亚银弓最好属性 银弓最高品质是什么

泰拉瑞亚钨弓怎么制作 钨弓最好附魔是什么

泰拉瑞亚钨弓怎么制作 钨弓最好附魔是什么

泰拉瑞亚金弓有什么用 金弓好吗有什么用

泰拉瑞亚金弓有什么用 金弓好吗有什么用

泰拉瑞亚铂金弓怎么做 铂金弓秒伤多少

泰拉瑞亚铂金弓怎么做 铂金弓秒伤多少

泰拉瑞亚恶魔弓怎么获得 恶魔弓厉害吗怎么做

泰拉瑞亚恶魔弓怎么获得 恶魔弓厉害吗怎么做

泰拉瑞亚肌腱弓最高附魔 肌腱弓怎么样好吗

泰拉瑞亚肌腱弓最高附魔 肌腱弓怎么样好吗

泰拉瑞亚蜂膝弓怎么样 蜂膝弓附魔最好是什么

泰拉瑞亚蜂膝弓怎么样 蜂膝弓附魔最好是什么

泰拉瑞亚地狱之翼弓怎么做怎么获得

泰拉瑞亚地狱之翼弓怎么做怎么获得

泰拉瑞亚熔火之怒怎么合成获得 熔火之怒最好附魔是什么

泰拉瑞亚熔火之怒怎么合成获得 熔火之怒最好附魔是什么

泰拉瑞亚珍珠木弓怎么样怎么获得

泰拉瑞亚珍珠木弓怎么样怎么获得

泰拉瑞亚骸骨弓怎么获得 骸骨弓有什么用

泰拉瑞亚骸骨弓怎么获得 骸骨弓有什么用

泰拉瑞亚冰雪弓附魔最好是什么 冰弓怎么获得

泰拉瑞亚冰雪弓附魔最好是什么 冰弓怎么获得

泰拉瑞亚代达罗斯风暴弓怎么弄 代达罗斯风暴弓用什么箭最好

泰拉瑞亚代达罗斯风暴弓怎么弄 代达罗斯风暴弓用什么箭最好

泰拉瑞亚暗影焰弓好吗 暗影焰弓最好附魔是什么

泰拉瑞亚暗影焰弓好吗 暗影焰弓最好附魔是什么

泰拉瑞亚幽灵凤凰怎么得 幽灵凤凰附魔最好是什么

泰拉瑞亚幽灵凤凰怎么得 幽灵凤凰附魔最好是什么

泰拉瑞亚脉冲弓怎么获得 脉冲弓是专家模式的武器吗

泰拉瑞亚脉冲弓怎么获得 脉冲弓是专家模式的武器吗

泰拉瑞亚空中祸害怎么得怎么样 空中祸害厉害吗

泰拉瑞亚空中祸害怎么得怎么样 空中祸害厉害吗

泰拉瑞亚海啸弓配什么箭 海啸弓附魔最好是什么

泰拉瑞亚海啸弓配什么箭 海啸弓附魔最好是什么

泰拉瑞亚幻影弓怎么获得怎么做 幻影弓最好附魔是什么

泰拉瑞亚幻影弓怎么获得怎么做 幻影弓最好附魔是什么

泰拉瑞亚钴连弩怎么样如何获得 钴蓝连弩详细介绍

泰拉瑞亚钴连弩怎么样如何获得 钴蓝连弩详细介绍

泰拉瑞亚钯金连弩怎么获得 钯金连弩好吗

泰拉瑞亚钯金连弩怎么获得 钯金连弩好吗

泰拉瑞亚秘银连弩怎么制作 秘银连弩好吗

泰拉瑞亚秘银连弩怎么制作 秘银连弩好吗

泰拉瑞亚山铜连弩好吗怎么制作 山铜连弩详细攻略

泰拉瑞亚山铜连弩好吗怎么制作 山铜连弩详细攻略

泰拉瑞亚精金连弩附魔最好是什么 精金连弩详细攻略

泰拉瑞亚精金连弩附魔最好是什么 精金连弩详细攻略

泰拉瑞亚钛金连弩怎么做 钛金连弩最好附魔是什么

泰拉瑞亚钛金连弩怎么做 钛金连弩最好附魔是什么

泰拉瑞亚神圣连弩能合成什么 神圣连弩厉害吗

泰拉瑞亚神圣连弩能合成什么 神圣连弩厉害吗

泰拉瑞亚叶绿连弩最好附魔是什么 叶绿连弩和巨兽鲨哪个好

泰拉瑞亚叶绿连弩最好附魔是什么 叶绿连弩和巨兽鲨哪个好

泰拉瑞亚尖桩发射器怎么获得 尖桩发射器最好附魔是什么

泰拉瑞亚尖桩发射器怎么获得 尖桩发射器最好附魔是什么

泰拉瑞亚红莱德枪有什么用 红莱德枪子弹用什么

泰拉瑞亚红莱德枪有什么用 红莱德枪子弹用什么

泰拉瑞亚迷你鲨能合成什么 迷你鲨附魔最好是什么

泰拉瑞亚迷你鲨能合成什么 迷你鲨附魔最好是什么

泰拉瑞亚燧发枪有什么用 燧发枪详细攻略

泰拉瑞亚燧发枪有什么用 燧发枪详细攻略

泰拉瑞亚火枪怎么样怎么获得 火枪子弹怎么获得

泰拉瑞亚火枪怎么样怎么获得 火枪子弹怎么获得

泰拉瑞亚夺命枪怎么样 夺命枪子弹怎么获得

泰拉瑞亚夺命枪怎么样 夺命枪子弹怎么获得

泰拉瑞亚左轮手枪厉害吗怎么得 左轮手枪介绍

泰拉瑞亚左轮手枪厉害吗怎么得 左轮手枪介绍

泰拉瑞亚三发猎枪怎么得 三发猎枪可以合成什么

泰拉瑞亚三发猎枪怎么得 三发猎枪可以合成什么

泰拉瑞亚手枪怎么获得厉害吗 手枪可以合成什么

泰拉瑞亚手枪怎么获得厉害吗 手枪可以合成什么

泰拉瑞亚星星炮好用吗怎么获得 星星炮合成攻略

泰拉瑞亚星星炮好用吗怎么获得 星星炮合成攻略

泰拉瑞亚发条式突击步枪怎么获得 最好的附魔是什么

泰拉瑞亚发条式突击步枪怎么获得 最好的附魔是什么

泰拉瑞亚鳄鱼机关枪和巨兽鲨哪个好 鳄鱼机关枪怎么获得

泰拉瑞亚鳄鱼机关枪和巨兽鲨哪个好 鳄鱼机关枪怎么获得

泰拉瑞亚霰弹枪怎么获得怎么合成 霰弹枪详细介绍

泰拉瑞亚霰弹枪怎么获得怎么合成 霰弹枪详细介绍

泰拉瑞亚玛瑙爆破枪怎么合成 玛瑙爆破枪配方介绍

泰拉瑞亚玛瑙爆破枪怎么合成 玛瑙爆破枪配方介绍

泰拉瑞亚钱币枪怎么获得 钱币枪厉害吗

泰拉瑞亚钱币枪怎么获得 钱币枪厉害吗

泰拉瑞亚乌兹冲锋枪和巨兽鲨哪个好 乌兹冲锋枪附魔

泰拉瑞亚乌兹冲锋枪和巨兽鲨哪个好 乌兹冲锋枪附魔

泰拉瑞亚巨兽鲨怎么做用什么子弹 巨兽鲨附魔

泰拉瑞亚巨兽鲨怎么做用什么子弹 巨兽鲨附魔

泰拉瑞亚维纳斯万能枪怎么获得 维纳斯万能枪厉害吗

泰拉瑞亚维纳斯万能枪怎么获得 维纳斯万能枪厉害吗

泰拉瑞亚战术霰弹枪怎么获得 战术霰弹枪附魔最好是什么

泰拉瑞亚战术霰弹枪怎么获得 战术霰弹枪附魔最好是什么

泰拉瑞亚狙击步枪最好附魔是什么 狙击步枪怎么获得

泰拉瑞亚狙击步枪最好附魔是什么 狙击步枪怎么获得

泰拉瑞亚玉米糖步枪子弹怎么获得 玉米糖步枪介绍

泰拉瑞亚玉米糖步枪子弹怎么获得 玉米糖步枪介绍

泰拉瑞亚链式机枪怎么获得 链式机枪附魔最好是什么

泰拉瑞亚链式机枪怎么获得 链式机枪附魔最好是什么

泰拉瑞亚外星气泡枪怎么获得 外星霰弹枪好用吗

泰拉瑞亚外星气泡枪怎么获得 外星霰弹枪好用吗

泰拉瑞亚星旋机枪怎么合成 星旋机枪附魔最好是什么

泰拉瑞亚星旋机枪怎么合成 星旋机枪附魔最好是什么

泰拉瑞亚太空海豚机枪最高附魔是什么 太空海豚机枪介绍攻略

泰拉瑞亚太空海豚机枪最高附魔是什么 太空海豚机枪介绍攻略

泰拉瑞亚毒刺发射器好吗 毒刺发射器子弹怎么获得

泰拉瑞亚毒刺发射器好吗 毒刺发射器子弹怎么获得

泰拉瑞亚手榴弹发射器附魔最好是什么 手榴弹发射器子弹

泰拉瑞亚手榴弹发射器附魔最好是什么 手榴弹发射器子弹

泰拉瑞亚感应雷发射器怎么用怎么获得 感应雷发射器子弹

泰拉瑞亚感应雷发射器怎么用怎么获得 感应雷发射器子弹

泰拉瑞亚火箭发射器附魔最好是什么 火箭发射器子弹怎么得

泰拉瑞亚火箭发射器附魔最好是什么 火箭发射器子弹怎么得

泰拉瑞亚钉枪最佳附魔是什么 钉枪的子弹是什么

泰拉瑞亚钉枪最佳附魔是什么 钉枪的子弹是什么

泰拉瑞亚喜庆弹射器怎么用 喜庆弹射器用什么子弹

泰拉瑞亚喜庆弹射器怎么用 喜庆弹射器用什么子弹

泰拉瑞亚电圈发射器怎么用 电圈发射器用什么子弹

泰拉瑞亚电圈发射器怎么用 电圈发射器用什么子弹

泰拉瑞亚雪人炮弹药子弹是什么 雪人炮怎么获得

泰拉瑞亚雪人炮弹药子弹是什么 雪人炮怎么获得

泰拉瑞亚杰克南瓜灯发射器子弹怎么获得 杰克南瓜灯发射器介绍

泰拉瑞亚杰克南瓜灯发射器子弹怎么获得 杰克南瓜灯发射器介绍

泰拉瑞亚信号枪有什么用 信号枪可以召唤军火商NPC吗?

泰拉瑞亚信号枪有什么用 信号枪可以召唤军火商NPC吗?

泰拉瑞亚吹管怎么做怎么用 吹管详细介绍

泰拉瑞亚吹管怎么做怎么用 吹管详细介绍

泰拉瑞亚吹箭筒的弹药是什么 吹箭筒怎么获得介绍

泰拉瑞亚吹箭筒的弹药是什么 吹箭筒怎么获得介绍

泰拉瑞亚沙枪的弹药是什么 沙枪怎么合成获得

泰拉瑞亚沙枪的弹药是什么 沙枪怎么合成获得

泰拉瑞亚鱼叉枪有什么用 鱼叉枪如何获得

泰拉瑞亚鱼叉枪有什么用 鱼叉枪如何获得

泰拉瑞亚彩弹枪怎么获得 彩弹枪掉率高吗

泰拉瑞亚彩弹枪怎么获得 彩弹枪掉率高吗

泰拉瑞亚史莱姆枪有什么用 史莱姆枪强化介绍

泰拉瑞亚史莱姆枪有什么用 史莱姆枪强化介绍

泰拉瑞亚水枪有什么用可以干什么

泰拉瑞亚水枪有什么用可以干什么

泰拉瑞亚飞镖手枪怎么做怎么获得 射镖手枪用什么子弹

泰拉瑞亚飞镖手枪怎么做怎么获得 射镖手枪用什么子弹

泰拉瑞亚飞镖步枪怎么做 飞镖枪子弹弹药是什么

泰拉瑞亚飞镖步枪怎么做 飞镖枪子弹弹药是什么

泰拉瑞亚火焰喷射器怎么获得 火焰喷射器子弹是什么

泰拉瑞亚火焰喷射器怎么获得 火焰喷射器子弹是什么

泰拉瑞亚食人鱼枪怎么获得 食人鱼枪附魔最好是什么

泰拉瑞亚食人鱼枪怎么获得 食人鱼枪附魔最好是什么

泰拉瑞亚火花魔棒有啥用怎么获得

泰拉瑞亚火花魔棒有啥用怎么获得

泰拉瑞亚紫晶法杖有什么用怎么获得

泰拉瑞亚紫晶法杖有什么用怎么获得

泰拉瑞亚蓝玉法杖怎么获得厉害吗

泰拉瑞亚蓝玉法杖怎么获得厉害吗

泰拉瑞亚黄玉法杖怎么做怎么获得

泰拉瑞亚黄玉法杖怎么做怎么获得

泰拉瑞亚翡翠法杖需要什么怎么获得

泰拉瑞亚翡翠法杖需要什么怎么获得

泰拉瑞亚红玉法杖怎么获得 红玉法杖详细攻略

泰拉瑞亚红玉法杖怎么获得 红玉法杖详细攻略

泰拉瑞亚钻石法杖怎么样 钻石法杖合成方式分享

泰拉瑞亚钻石法杖怎么样 钻石法杖合成方式分享

泰拉瑞亚琥珀法杖怎么获得厉害吗

泰拉瑞亚琥珀法杖怎么获得厉害吗

泰拉瑞亚魔刺怎么得有什么用 魔刺最好的效果

泰拉瑞亚魔刺怎么得有什么用 魔刺最好的效果

泰拉瑞亚猩红魔杖最高附魔是什么 猩红魔杖详细介绍

泰拉瑞亚猩红魔杖最高附魔是什么 猩红魔杖详细介绍

泰拉瑞亚魔法导弹可以合成什么 魔法导弹怎么做

泰拉瑞亚魔法导弹可以合成什么 魔法导弹怎么做

泰拉瑞亚海蓝权杖能合成什么 海蓝权杖有什么用

泰拉瑞亚海蓝权杖能合成什么 海蓝权杖有什么用

泰拉瑞亚烈火神鞭有什么用 烈焰火鞭怎么获得

泰拉瑞亚烈火神鞭有什么用 烈焰火鞭怎么获得

泰拉瑞亚火之花武器怎么获得 火之花最高附魔是什么

泰拉瑞亚火之花武器怎么获得 火之花最高附魔是什么

泰拉瑞亚寒霜之花怎么获得 寒霜之花属性介绍

泰拉瑞亚寒霜之花怎么获得 寒霜之花属性介绍

泰拉瑞亚魔晶碎块有什么用 魔晶碎块武器好用吗

泰拉瑞亚魔晶碎块有什么用 魔晶碎块武器好用吗

泰拉瑞亚夺命杖怎么得 夺命杖如何能吸血

泰拉瑞亚夺命杖怎么得 夺命杖如何能吸血

泰拉瑞亚雨云魔杖最好附魔是什么 雨云魔杖怎么获得

泰拉瑞亚雨云魔杖最好附魔是什么 雨云魔杖怎么获得

泰拉瑞亚剧毒法杖合成升级成什么 剧毒法杖攻略

泰拉瑞亚剧毒法杖合成升级成什么 剧毒法杖攻略

泰拉瑞亚流星法杖好不好怎么做

泰拉瑞亚流星法杖好不好怎么做

泰拉瑞亚寒霜法杖怎么获得 寒霜法杖最高附魔是什么

泰拉瑞亚寒霜法杖怎么获得 寒霜法杖最高附魔是什么

泰拉瑞亚毒液法杖附魔最好是什么 毒液法杖怎么做

泰拉瑞亚毒液法杖附魔最好是什么 毒液法杖怎么做

泰拉瑞亚无限智慧巨著是什么厉害吗

泰拉瑞亚无限智慧巨著是什么厉害吗

泰拉瑞亚彩虹魔杖怎么做 彩虹魔杖附魔最好是什么

泰拉瑞亚彩虹魔杖怎么做 彩虹魔杖附魔最好是什么

泰拉瑞亚狱火叉怎么得 狱火叉附魔最好是什么

泰拉瑞亚狱火叉怎么得 狱火叉附魔最好是什么

泰拉瑞亚暗影束法杖爆率高吗好用吗 暗影束法杖怎么得

泰拉瑞亚暗影束法杖爆率高吗好用吗 暗影束法杖怎么得

泰拉瑞亚爆裂藤蔓最好附魔是什么 爆裂藤蔓进化合成荆棘藤蔓

泰拉瑞亚爆裂藤蔓最好附魔是什么 爆裂藤蔓进化合成荆棘藤蔓

泰拉瑞亚蝙蝠权杖最高附魔是什么 蝙蝠权杖介绍

泰拉瑞亚蝙蝠权杖最高附魔是什么 蝙蝠权杖介绍

泰拉瑞亚大地法杖怎么获得 大地法杖附魔最好是什么

泰拉瑞亚大地法杖怎么获得 大地法杖附魔最好是什么

泰拉瑞亚幽灵法杖附魔最好品质是什么 幽灵法杖怎么得

泰拉瑞亚幽灵法杖附魔最好品质是什么 幽灵法杖怎么得

泰拉瑞亚双足翼龙怒气怎么获 双足翼龙怒气附魔得厉害吗

泰拉瑞亚双足翼龙怒气怎么获 双足翼龙怒气附魔得厉害吗

泰拉瑞亚暴雪法杖最高附魔是什么 暴雪法杖怎么用

泰拉瑞亚暴雪法杖最高附魔是什么 暴雪法杖怎么用

泰拉瑞亚太空枪最好属性 太空枪怎么做

泰拉瑞亚太空枪最好属性 太空枪怎么做

泰拉瑞亚蜜蜂枪怎么打肉山 蜜蜂枪怎么做厉害吗

泰拉瑞亚蜜蜂枪怎么打肉山 蜜蜂枪怎么做厉害吗

泰拉瑞亚激光步枪怎么得 激光步枪附魔最好是什么

泰拉瑞亚激光步枪怎么得 激光步枪附魔最好是什么

泰拉瑞亚胡蜂枪怎么获得 胡蜂枪附魔最好是什么

泰拉瑞亚胡蜂枪怎么获得 胡蜂枪附魔最好是什么

泰拉瑞亚吹叶机最好附魔是什么 吹叶机怎么得

泰拉瑞亚吹叶机最好附魔是什么 吹叶机怎么得

泰拉瑞亚高温射线枪怎么获得 热能射线厉害吗

泰拉瑞亚高温射线枪怎么获得 热能射线厉害吗

泰拉瑞亚带电爆破炮怎么制作 充能爆破炮怎么获得

泰拉瑞亚带电爆破炮怎么制作 充能爆破炮怎么获得

泰拉瑞亚激光机枪最高附魔是什么 激光机枪怎么获得

泰拉瑞亚激光机枪最高附魔是什么 激光机枪怎么获得

泰拉瑞亚泡泡枪怎么获得这么细学 泡泡枪最高附魔

泰拉瑞亚泡泡枪怎么获得这么细学 泡泡枪最高附魔

泰拉瑞亚恶魔锄刀厉害吗 恶魔镰刀附魔最好是什么

泰拉瑞亚恶魔锄刀厉害吗 恶魔镰刀附魔最好是什么

泰拉瑞亚水矢附魔最好是什么 水矢之书在哪里怎么得

泰拉瑞亚水矢附魔最好是什么 水矢之书在哪里怎么得

泰拉瑞亚骷髅头法书有什么用怎么获得

泰拉瑞亚骷髅头法书有什么用怎么获得

泰拉瑞亚水晶风暴厉害吗 水晶风暴怎么获得

泰拉瑞亚水晶风暴厉害吗 水晶风暴怎么获得

泰拉瑞亚黄金雨怎么做 黄金雨魔法书合成方式

泰拉瑞亚黄金雨怎么做 黄金雨魔法书合成方式

泰拉瑞亚诅咒焰怎么获得有什么用 诅咒焰魔法书介绍

泰拉瑞亚诅咒焰怎么获得有什么用 诅咒焰魔法书介绍

泰拉瑞亚磁球魔法书怎么获得 磁球最高附魔是什么

泰拉瑞亚磁球魔法书怎么获得 磁球最高附魔是什么

泰拉瑞亚月耀最高附魔 月耀怎么获得详细介绍

泰拉瑞亚月耀最高附魔 月耀怎么获得详细介绍

泰拉瑞亚利刃台风最高附魔是什么 利刃台风怎么获得

泰拉瑞亚利刃台风最高附魔是什么 利刃台风怎么获得

泰拉瑞亚蛇发女妖头有什么用怎么获得

泰拉瑞亚蛇发女妖头有什么用怎么获得

泰拉瑞亚裂天剑怎么合成怎么得 裂天剑好不好

泰拉瑞亚裂天剑怎么合成怎么得 裂天剑好不好

泰拉瑞亚魔法飞刀最好附魔 魔法飞刀怎么获得

泰拉瑞亚魔法飞刀最好附魔 魔法飞刀怎么获得

泰拉瑞亚水晶蛇怎么获得怎么钓 水晶蛇钓率高吗

泰拉瑞亚水晶蛇怎么获得怎么钓 水晶蛇钓率高吗

泰拉瑞亚神灯烈焰怎么使用 神灯烈焰在哪合成

泰拉瑞亚神灯烈焰怎么使用 神灯烈焰在哪合成

泰拉瑞亚暗影焰妖娃好吗 暗影焰妖娃怎么获得

泰拉瑞亚暗影焰妖娃好吗 暗影焰妖娃怎么获得

泰拉瑞亚魔法竖琴合成怎么做 魔法竖琴有什么用

泰拉瑞亚魔法竖琴合成怎么做 魔法竖琴有什么用

泰拉瑞亚毒气瓶怎么得到 毒气瓶最高附魔是什么

泰拉瑞亚毒气瓶怎么得到 毒气瓶最高附魔是什么

泰拉瑞亚邪恶三叉戟怎么获得 邪恶三叉戟附魔

泰拉瑞亚邪恶三叉戟怎么获得 邪恶三叉戟附魔

泰拉瑞亚终极棱镜怎么得 终极棱镜最高品质是什么

泰拉瑞亚终极棱镜怎么得 终极棱镜最高品质是什么

泰拉瑞亚剃刀松怎么得 剃刀松附魔最好是什么

泰拉瑞亚剃刀松怎么得 剃刀松附魔最好是什么

泰拉瑞亚星云奥秘和星云烈焰哪个好 星云奥秘附魔

泰拉瑞亚星云奥秘和星云烈焰哪个好 星云奥秘附魔

泰拉瑞亚星云烈焰和星云奥秘哪个好 星云烈焰最好附魔

泰拉瑞亚星云烈焰和星云奥秘哪个好 星云烈焰最好附魔

泰拉瑞亚史莱姆法杖怎么刷怎么获得 史莱姆法杖详细介绍

泰拉瑞亚史莱姆法杖怎么刷怎么获得 史莱姆法杖详细介绍

泰拉瑞亚黄蜂法杖怎么获得 黄蜂法杖附魔最好是什么

泰拉瑞亚黄蜂法杖怎么获得 黄蜂法杖附魔最好是什么

泰拉瑞亚小鬼法杖怎么获得 小鬼法杖可以召唤几个

泰拉瑞亚小鬼法杖怎么获得 小鬼法杖可以召唤几个

泰拉瑞亚魔眼法杖怎么做 魔眼法杖附魔最高是什么

泰拉瑞亚魔眼法杖怎么做 魔眼法杖附魔最高是什么

泰拉瑞亚海盗法杖怎么得 海盗法杖好吗

泰拉瑞亚海盗法杖怎么得 海盗法杖好吗

泰拉瑞亚致命球法杖三种形态 致命球法杖好用吗

泰拉瑞亚致命球法杖三种形态 致命球法杖好用吗

泰拉瑞亚蜘蛛法杖怎么得 蜘蛛法杖好吗

泰拉瑞亚蜘蛛法杖怎么得 蜘蛛法杖好吗

泰拉瑞亚矮人法杖怎么获得 矮人法杖可以召唤几个

泰拉瑞亚矮人法杖怎么获得 矮人法杖可以召唤几个

泰拉瑞亚乌鸦法杖怎么得 乌鸦法杖好用吗

泰拉瑞亚乌鸦法杖怎么得 乌鸦法杖好用吗

泰拉瑞亚外星法杖强吗怎么样 外星法杖附魔攻略

泰拉瑞亚外星法杖强吗怎么样 外星法杖附魔攻略

泰拉瑞亚暴风雨法杖最好附魔是什么 暴风雨法杖前缀

泰拉瑞亚暴风雨法杖最好附魔是什么 暴风雨法杖前缀

泰拉瑞亚星尘之龙法杖好吗怎么获得

泰拉瑞亚星尘之龙法杖好吗怎么获得

泰拉瑞亚星尘细胞法杖附魔最好是什么 星尘细胞法杖攻略

泰拉瑞亚星尘细胞法杖附魔最好是什么 星尘细胞法杖攻略

泰拉瑞亚神奇宝贝mod介绍下载 泰拉瑞亚宠物小精灵mod

泰拉瑞亚神奇宝贝mod介绍下载 泰拉瑞亚宠物小精灵mod

泰拉瑞亚灾厄mod汉化版下载 泰拉瑞亚灾厄mod怎么安装

泰拉瑞亚灾厄mod汉化版下载 泰拉瑞亚灾厄mod怎么安装

泰拉瑞亚瑟银mod介绍下载 瑟银Thorium mod中文版

泰拉瑞亚瑟银mod介绍下载 瑟银Thorium mod中文版

泰拉瑞亚1.4旅程的终点 更新变动总览

泰拉瑞亚1.4旅程的终点 更新变动总览

泰拉瑞亚墓地生物群落怎么生成 墓地生物群落介绍

泰拉瑞亚墓地生物群落怎么生成 墓地生物群落介绍

泰拉瑞亚绿洲在哪 绿洲生物群落介绍

泰拉瑞亚绿洲在哪 绿洲生物群落介绍

泰拉瑞亚仙人掌镐怎么做 仙人掌镐有铜镐好用吗

泰拉瑞亚仙人掌镐怎么做 仙人掌镐有铜镐好用吗

泰拉瑞亚铁镐怎么做 铁镐可以挖陨石吗

泰拉瑞亚铁镐怎么做 铁镐可以挖陨石吗

泰拉瑞亚铜镐怎么做 铜镐怎么升级合成

泰拉瑞亚铜镐怎么做 铜镐怎么升级合成

泰拉瑞亚锡镐怎么做怎么合成 锡镐要在哪里做

泰拉瑞亚锡镐怎么做怎么合成 锡镐要在哪里做

泰拉瑞亚铅镐怎么做 铅镐可以开采哪些矿

泰拉瑞亚铅镐怎么做 铅镐可以开采哪些矿

泰拉瑞亚银镐怎么做 银镐可以挖陨石矿吗

泰拉瑞亚银镐怎么做 银镐可以挖陨石矿吗

泰拉瑞亚骨镐id 骨镐怎么做怎么合成获得

泰拉瑞亚骨镐id 骨镐怎么做怎么合成获得

泰拉瑞亚钨镐怎么做怎么合成 钨镐能挖什么

泰拉瑞亚钨镐怎么做怎么合成 钨镐能挖什么

泰拉瑞亚1.4大师模式和专家模式的区别 大师模式独有物品

泰拉瑞亚1.4大师模式和专家模式的区别 大师模式独有物品

泰拉瑞亚天顶剑怎么做 天顶剑最好附魔合成表分享

泰拉瑞亚天顶剑怎么做 天顶剑最好附魔合成表分享

泰拉瑞亚毕业战士装备搭配分享 天顶剑+日曜套+不明飞行物

泰拉瑞亚毕业战士装备搭配分享 天顶剑+日曜套+不明飞行物

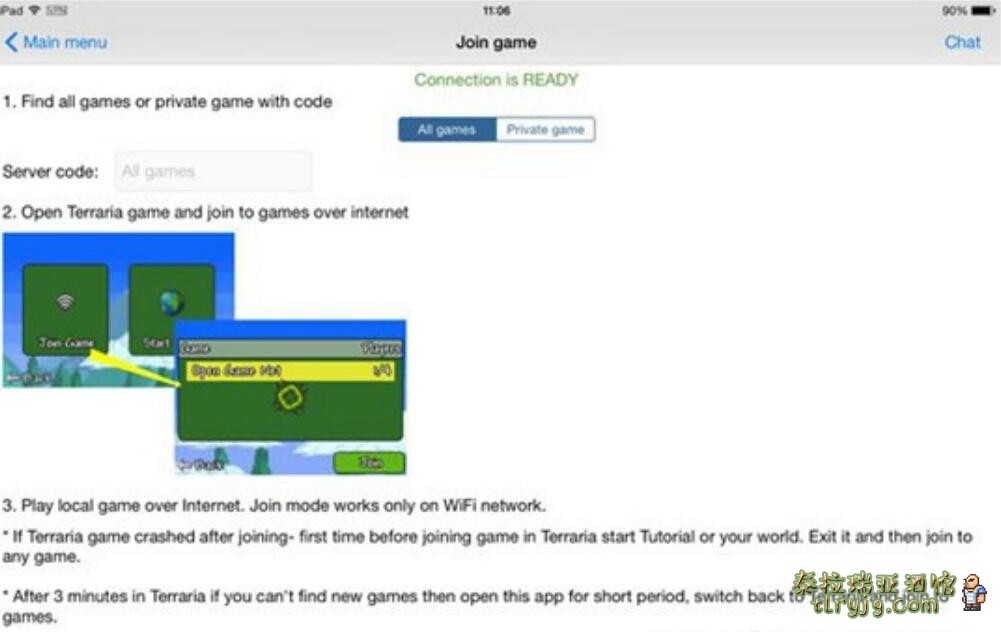

泰拉瑞亚IOS怎么远程联机 泰拉瑞亚联机方法分享

泰拉瑞亚IOS怎么远程联机 泰拉瑞亚联机方法分享

泰拉瑞亚翅膀排行榜 翅膀制作方法大全

泰拉瑞亚翅膀排行榜 翅膀制作方法大全

泰拉瑞亚手机怎么合成 手机有什么用攻略详解

泰拉瑞亚手机怎么合成 手机有什么用攻略详解

泰拉瑞亚射手毕业装备饰品 射手毕业套装顺序分享

泰拉瑞亚射手毕业装备饰品 射手毕业套装顺序分享

泰拉瑞亚法师毕业饰品装备 法师毕业套装分享

泰拉瑞亚法师毕业饰品装备 法师毕业套装分享

泰拉瑞亚机械蠕虫打法攻略 机械蠕虫怎么打

泰拉瑞亚机械蠕虫打法攻略 机械蠕虫怎么打

泰拉瑞亚最稀有时装分享 泰拉瑞亚开发者套装怎么获得

泰拉瑞亚最稀有时装分享 泰拉瑞亚开发者套装怎么获得

泰拉瑞亚召唤师毕业装备1.4 召唤师毕业饰品套装

泰拉瑞亚召唤师毕业装备1.4 召唤师毕业饰品套装

泰拉瑞亚挖掘机合成表 挖掘机座骑怎么获得合成

泰拉瑞亚挖掘机合成表 挖掘机座骑怎么获得合成

泰拉瑞亚机械骷髅王怎么打 机械骷髅王打法攻略

泰拉瑞亚机械骷髅王怎么打 机械骷髅王打法攻略

泰拉瑞亚怎么开服务器联机玩 最简单的开服教程

泰拉瑞亚怎么开服务器联机玩 最简单的开服教程

泰拉瑞亚月总后干嘛 击败boss月球领主后该干什么

泰拉瑞亚月总后干嘛 击败boss月球领主后该干什么

泰拉瑞亚游戏肉山后的套装顺序是怎样的

泰拉瑞亚游戏肉山后的套装顺序是怎样的

泰拉瑞亚肉山后怎么玩 泰拉瑞亚肉山后攻略

泰拉瑞亚肉山后怎么玩 泰拉瑞亚肉山后攻略

泰拉瑞亚前期开荒怎么玩什么装备好 前期开荒攻略

泰拉瑞亚前期开荒怎么玩什么装备好 前期开荒攻略

泰拉瑞亚游戏里有哪些神器 泰拉瑞亚神器排行

泰拉瑞亚游戏里有哪些神器 泰拉瑞亚神器排行

泰拉瑞亚中有哪些有趣的彩蛋 泰拉瑞亚有彩蛋吗

泰拉瑞亚中有哪些有趣的彩蛋 泰拉瑞亚有彩蛋吗

泰拉瑞亚状态信息大全 泰拉瑞亚游戏提示信息汇总

泰拉瑞亚状态信息大全 泰拉瑞亚游戏提示信息汇总

泰拉瑞亚打肉山前需要做好什么准备 肉山怎么打攻略

泰拉瑞亚打肉山前需要做好什么准备 肉山怎么打攻略

泰拉瑞亚化石镐怎么获得 化石镐有什么用

泰拉瑞亚化石镐怎么获得 化石镐有什么用

泰拉瑞亚棒棒糖镐怎么得 糖棒镐有什么用

泰拉瑞亚棒棒糖镐怎么得 糖棒镐有什么用

泰拉瑞亚金镐怎么合成能挖什么 金镐上一级是什么

泰拉瑞亚金镐怎么合成能挖什么 金镐上一级是什么

泰拉瑞亚铂金镐能挖什么矿 铂金镐怎么合成获得

泰拉瑞亚铂金镐能挖什么矿 铂金镐怎么合成获得

泰拉瑞亚梦魇镐能挖什么矿怎么获得 梦魇镐合成方式分享

泰拉瑞亚梦魇镐能挖什么矿怎么获得 梦魇镐合成方式分享

泰拉瑞亚死亡使者镐怎么合成怎么弄 死亡使者镐合成方式

泰拉瑞亚死亡使者镐怎么合成怎么弄 死亡使者镐合成方式

泰拉瑞亚熔岩镐怎么做能挖什么 熔岩镐合成方式分享

泰拉瑞亚熔岩镐怎么做能挖什么 熔岩镐合成方式分享

泰拉瑞亚掠夺鲨怎么获得有什么用 掠夺鲨获得方式

泰拉瑞亚掠夺鲨怎么获得有什么用 掠夺鲨获得方式

泰拉瑞亚钴镐可以挖什么有什么用 钴镐合成方式获得

泰拉瑞亚钴镐可以挖什么有什么用 钴镐合成方式获得

泰拉瑞亚钯金镐怎么做能挖什么 钯金镐合成方式

泰拉瑞亚钯金镐怎么做能挖什么 钯金镐合成方式

泰拉瑞亚秘银镐怎么合成 秘银镐和秘银钻头哪个好

泰拉瑞亚秘银镐怎么合成 秘银镐和秘银钻头哪个好

泰拉瑞亚山铜镐怎么做在哪里合成 山铜镐合成方式

泰拉瑞亚山铜镐怎么做在哪里合成 山铜镐合成方式

泰拉瑞亚精金镐能挖什么有什么用 精金镐合成方式

泰拉瑞亚精金镐能挖什么有什么用 精金镐合成方式

泰拉瑞亚钛金镐能挖叶绿吗 钛金镐合成方式分享

泰拉瑞亚钛金镐能挖叶绿吗 钛金镐合成方式分享

泰拉瑞亚叶绿镐能挖什么有什么用 叶绿镐合成方式

泰拉瑞亚叶绿镐能挖什么有什么用 叶绿镐合成方式

泰拉瑞亚幽灵镐怎么做有什么用 幽灵镐合成方式

泰拉瑞亚幽灵镐怎么做有什么用 幽灵镐合成方式

泰拉瑞亚夜明镐怎么获得 耀斑镐+星旋镐+星云镐+星尘镐合成方法

泰拉瑞亚夜明镐怎么获得 耀斑镐+星旋镐+星云镐+星尘镐合成方法

泰拉瑞亚叶绿钻头能挖什么怎么用 叶绿钻头id和获取方法

泰拉瑞亚叶绿钻头能挖什么怎么用 叶绿钻头id和获取方法

泰拉瑞亚钛金钻头能挖什么怎么合成 钛金钻头id和获取方式

泰拉瑞亚钛金钻头能挖什么怎么合成 钛金钻头id和获取方式

泰拉瑞亚精金钻头可以挖什么有什么用 精金钻头物品id和获取方式

泰拉瑞亚精金钻头可以挖什么有什么用 精金钻头物品id和获取方式

泰拉瑞亚山铜钻头能挖什么怎么做 山铜钻头合成方式

泰拉瑞亚山铜钻头能挖什么怎么做 山铜钻头合成方式

泰拉瑞亚秘银钻头怎么做能挖什么 秘银钻头id合成方式

泰拉瑞亚秘银钻头怎么做能挖什么 秘银钻头id合成方式

泰拉瑞亚钯金钻头和镐的区别 钯金钻头怎么做能挖什么

泰拉瑞亚钯金钻头和镐的区别 钯金钻头怎么做能挖什么

泰拉瑞亚钴钻头和钴镐哪个好 钴钻头怎么做能挖什么

泰拉瑞亚钴钻头和钴镐哪个好 钴钻头怎么做能挖什么

泰拉瑞亚掘墓者铲子怎么做 掘墓者铁铲物品id合成方式

泰拉瑞亚掘墓者铲子怎么做 掘墓者铁铲物品id合成方式

泰拉瑞亚铜斧头怎么做怎么合成 铜斧物品id获取方式

泰拉瑞亚铜斧头怎么做怎么合成 铜斧物品id获取方式

泰拉瑞亚箭锡斧怎么制作 锡斧id合成方式分享

泰拉瑞亚箭锡斧怎么制作 锡斧id合成方式分享

泰拉瑞亚铁斧头怎么做 铁斧id和获得方式分享

泰拉瑞亚铁斧头怎么做 铁斧id和获得方式分享

泰拉瑞亚铅斧怎么做有什么用 铅斧物品id和获得方式

泰拉瑞亚铅斧怎么做有什么用 铅斧物品id和获得方式

泰拉瑞亚银斧头怎么做怎么合成 银斧物品id和获取方式

泰拉瑞亚银斧头怎么做怎么合成 银斧物品id和获取方式

泰拉瑞亚钨斧怎么做怎么合成 钨斧物品id和获取方式

泰拉瑞亚钨斧怎么做怎么合成 钨斧物品id和获取方式

泰拉瑞亚金斧头怎么做怎么合成 金斧物品id和获取方式

泰拉瑞亚金斧头怎么做怎么合成 金斧物品id和获取方式

泰拉瑞亚铂金斧怎么做怎么获得 铂金斧物品id合成方式

泰拉瑞亚铂金斧怎么做怎么获得 铂金斧物品id合成方式

泰拉瑞亚钴蓝战斧怎么合成怎么做 钴战斧物品id分享

泰拉瑞亚钴蓝战斧怎么合成怎么做 钴战斧物品id分享

泰拉瑞亚钴链锯怎么合成 钴链锯物品id分享

泰拉瑞亚钴链锯怎么合成 钴链锯物品id分享

泰拉瑞亚锯齿鲨有什么用 锯齿鲨怎么合成

泰拉瑞亚锯齿鲨有什么用 锯齿鲨怎么合成

泰拉瑞亚暗夜战斧有什么用 暗夜战斧怎么合成物品id分享

泰拉瑞亚暗夜战斧有什么用 暗夜战斧怎么合成物品id分享

泰拉瑞亚嗜血狂斧怎么合成怎么获得 嗜血狂斧物品id分享

泰拉瑞亚嗜血狂斧怎么合成怎么获得 嗜血狂斧物品id分享

泰拉瑞亚钯金战斧怎么获得 钯金战斧物品id分享

泰拉瑞亚钯金战斧怎么获得 钯金战斧物品id分享

泰拉瑞亚钯金链锯怎么合成 钯金链锯物品id分享

泰拉瑞亚钯金链锯怎么合成 钯金链锯物品id分享

泰拉瑞亚秘银战斧怎么合成怎么获得 秘银战斧物品id分享

泰拉瑞亚秘银战斧怎么合成怎么获得 秘银战斧物品id分享

泰拉瑞亚秘银链锯物品id分享 秘银链锯怎么合成怎么获得

泰拉瑞亚秘银链锯物品id分享 秘银链锯怎么合成怎么获得

泰拉瑞亚山铜战斧怎么做 山铜战斧物品id合成方式

泰拉瑞亚山铜战斧怎么做 山铜战斧物品id合成方式

泰拉瑞亚山铜链锯怎么做 山铜链锯获取方式分享

泰拉瑞亚山铜链锯怎么做 山铜链锯获取方式分享

泰拉瑞亚精金战斧如何合成 精金战斧获得方式物品id

泰拉瑞亚精金战斧如何合成 精金战斧获得方式物品id

泰拉瑞亚精金链锯怎么获得 精金链锯合成方式分享

泰拉瑞亚精金链锯怎么获得 精金链锯合成方式分享

泰拉瑞亚流星锤斧有什么用怎么做 流星锤斧物品id

泰拉瑞亚流星锤斧有什么用怎么做 流星锤斧物品id

泰拉瑞亚钛金战斧怎么获得 钛金战斧有什么用

泰拉瑞亚钛金战斧怎么获得 钛金战斧有什么用

泰拉瑞亚钛金链锯有什么用 钛金链锯获取方式分享

泰拉瑞亚钛金链锯有什么用 钛金链锯获取方式分享

泰拉瑞亚镐斧怎么获得 镐斧和斧钻怎么做

泰拉瑞亚镐斧怎么获得 镐斧和斧钻怎么做

泰拉瑞亚斧钻怎么做能采什么矿 斧钻合成方式分享

泰拉瑞亚斧钻怎么做能采什么矿 斧钻合成方式分享

泰拉瑞亚叶绿链锯有什么用 叶绿链锯怎么获得

泰拉瑞亚叶绿链锯有什么用 叶绿链锯怎么获得

泰拉瑞亚叶绿巨斧有什么用 叶绿巨斧怎么做怎么获得

泰拉瑞亚叶绿巨斧有什么用 叶绿巨斧怎么做怎么获得

泰拉瑞亚锯刃镐最高附魔 锯刃镐怎么弄有什么用

泰拉瑞亚锯刃镐最高附魔 锯刃镐怎么弄有什么用

泰拉瑞亚蘑菇矿挖爪有什么用怎么做 蘑菇矿挖爪物品id

泰拉瑞亚蘑菇矿挖爪有什么用怎么做 蘑菇矿挖爪物品id

泰拉瑞亚屠夫链锯最高附魔 屠夫链锯怎么获得

泰拉瑞亚屠夫链锯最高附魔 屠夫链锯怎么获得

泰拉瑞亚熔岩锤斧怎么做 熔岩锤斧厉害吗

泰拉瑞亚熔岩锤斧怎么做 熔岩锤斧厉害吗

泰拉瑞亚血锤斧怎么做怎么获得 血锤斧物品id

泰拉瑞亚血锤斧怎么做怎么获得 血锤斧物品id

泰拉瑞亚夜明锤斧怎么得有什么用 夜明锤斧合成方式

泰拉瑞亚夜明锤斧怎么得有什么用 夜明锤斧合成方式

泰拉瑞亚幽灵锤斧有什么用怎么获得

泰拉瑞亚幽灵锤斧有什么用怎么获得

泰拉瑞亚吉他斧头怎么获得有什么用 吉他斧爆率分享

泰拉瑞亚吉他斧头怎么获得有什么用 吉他斧爆率分享

泰拉瑞亚木锤怎么做怎么获得 木锤有什么用

泰拉瑞亚木锤怎么做怎么获得 木锤有什么用

泰拉瑞亚红木锤怎么做怎么获得 红木锤物品id分享

泰拉瑞亚红木锤怎么做怎么获得 红木锤物品id分享

泰拉瑞亚棕榈木锤怎么合成怎么获得 棕榈木锤怎么样

泰拉瑞亚棕榈木锤怎么合成怎么获得 棕榈木锤怎么样

泰拉瑞亚针叶木锤怎么合成怎么获得 针叶木锤怎么样

泰拉瑞亚针叶木锤怎么合成怎么获得 针叶木锤怎么样

泰拉瑞亚铜锤子怎么做怎么获得 铜锤怎么样

泰拉瑞亚铜锤子怎么做怎么获得 铜锤怎么样

泰拉瑞亚锡锤怎么获得怎么合成 锡锤可以做什么

泰拉瑞亚锡锤怎么获得怎么合成 锡锤可以做什么

泰拉瑞亚铁锤有什么用 铁锤怎么获得怎么合成

泰拉瑞亚铁锤有什么用 铁锤怎么获得怎么合成

泰拉瑞亚乌木锤怎么获得怎么合成 乌木在哪有什么用

泰拉瑞亚乌木锤怎么获得怎么合成 乌木在哪有什么用

泰拉瑞亚暗影木锤怎么获得怎么合成 暗影木在哪

泰拉瑞亚暗影木锤怎么获得怎么合成 暗影木在哪

泰拉瑞亚铅锤怎么获得怎么合成 铅锤怎么样

泰拉瑞亚铅锤怎么获得怎么合成 铅锤怎么样

泰拉瑞亚珍珠木锤怎么获得怎么合成 珍珠木锤怎么样

泰拉瑞亚珍珠木锤怎么获得怎么合成 珍珠木锤怎么样

泰拉瑞亚银锤怎么获得怎么合成 银锤可以做什么

泰拉瑞亚银锤怎么获得怎么合成 银锤可以做什么

泰拉瑞亚钨锤怎么获得怎么合成 钨锤有什么用

泰拉瑞亚钨锤怎么获得怎么合成 钨锤有什么用

泰拉瑞亚金锤合成表 金锤有什么用

泰拉瑞亚金锤合成表 金锤有什么用

泰拉瑞亚魔锤有什么用 魔锤怎么获得

泰拉瑞亚魔锤有什么用 魔锤怎么获得

泰拉瑞亚血肉锤作用 血肉锤怎么获得

泰拉瑞亚血肉锤作用 血肉锤怎么获得

泰拉瑞亚铂金锤怎么做 铂金锤有什么用

泰拉瑞亚铂金锤怎么做 铂金锤有什么用

泰拉瑞亚岩鱼锤在哪怎么获得 岩鱼锤获得概率

泰拉瑞亚岩鱼锤在哪怎么获得 岩鱼锤获得概率

泰拉瑞亚神锤怎么获得 神锤能干嘛

泰拉瑞亚神锤怎么获得 神锤能干嘛

泰拉瑞亚蘑菇锤有什么用 蘑菇锤怎么得怎么做

泰拉瑞亚蘑菇锤有什么用 蘑菇锤怎么得怎么做

泰拉瑞亚叶绿战锤怎么获得 叶绿战锤有什么用怎么合成

泰拉瑞亚叶绿战锤怎么获得 叶绿战锤有什么用怎么合成

泰拉瑞亚叶绿手提钻有什么用 叶绿手提钻怎么获得

泰拉瑞亚叶绿手提钻有什么用 叶绿手提钻怎么获得

泰拉瑞亚抓钩怎么做怎么用 抓钩有什么用

泰拉瑞亚抓钩怎么做怎么用 抓钩有什么用

泰拉瑞亚紫晶钩有什么用 紫晶钩怎么做

泰拉瑞亚紫晶钩有什么用 紫晶钩怎么做

泰拉瑞亚松鼠钩怎么用有什么用 松鼠钩获得方式

泰拉瑞亚松鼠钩怎么用有什么用 松鼠钩获得方式

泰拉瑞亚黄玉钩怎么合成 黄玉钩物品id分享

泰拉瑞亚黄玉钩怎么合成 黄玉钩物品id分享

泰拉瑞亚蓝玉钩怎么用 蓝玉钩怎么合成怎么获得

泰拉瑞亚蓝玉钩怎么用 蓝玉钩怎么合成怎么获得

泰拉瑞亚翡翠钩爪怎么合成 翡翠钩爪怎么用

泰拉瑞亚翡翠钩爪怎么合成 翡翠钩爪怎么用

泰拉瑞亚红玉钩有什么用 红玉钩怎么做

泰拉瑞亚红玉钩有什么用 红玉钩怎么做

泰拉瑞亚钻石钩爪怎么做 钻石钩爪使用说明

泰拉瑞亚钻石钩爪怎么做 钻石钩爪使用说明

泰拉瑞亚琥珀钩爪怎么获得 琥珀钩爪使用说明

泰拉瑞亚琥珀钩爪怎么获得 琥珀钩爪使用说明

泰拉瑞亚蛛丝吊索怎么用 蛛丝吊索怎么获得怎么合成

泰拉瑞亚蛛丝吊索怎么用 蛛丝吊索怎么获得怎么合成

泰拉瑞亚骷髅王之手有什么用 骷髅王之手爆率是多少

泰拉瑞亚骷髅王之手有什么用 骷髅王之手爆率是多少

泰拉瑞亚史莱姆钩爪怎么用 史莱姆钩爪怎么合成

泰拉瑞亚史莱姆钩爪怎么用 史莱姆钩爪怎么合成

泰拉瑞亚鱼钩爪有什么用 鱼钩爪怎么获得怎么合成

泰拉瑞亚鱼钩爪有什么用 鱼钩爪怎么获得怎么合成

泰拉瑞亚常春藤鞭有什么用 常春藤钩子怎么合成怎么获得

泰拉瑞亚常春藤鞭有什么用 常春藤钩子怎么合成怎么获得

泰拉瑞亚蝙蝠钩爪怎么获得 蝙蝠钩爪掉率是多少

泰拉瑞亚蝙蝠钩爪怎么获得 蝙蝠钩爪掉率是多少

泰拉瑞亚糖棒钩怎么用 糖棒钩怎么获得怎么合成

泰拉瑞亚糖棒钩怎么用 糖棒钩怎么获得怎么合成

泰拉瑞亚双钩有什么用 双钩怎么做

泰拉瑞亚双钩有什么用 双钩怎么做

泰拉瑞亚失谐钩爪有什么用 失谐钩爪怎么合成怎么获得

泰拉瑞亚失谐钩爪有什么用 失谐钩爪怎么合成怎么获得

泰拉瑞亚刺钩有什么用 刺钩怎么合成怎么获得

泰拉瑞亚刺钩有什么用 刺钩怎么合成怎么获得

泰拉瑞亚荧光钩有什么用 荧光钩怎么得

泰拉瑞亚荧光钩有什么用 荧光钩怎么得

泰拉瑞亚蠕虫钩有什么用 蠕虫钩怎么得怎么做

泰拉瑞亚蠕虫钩有什么用 蠕虫钩怎么得怎么做

泰拉瑞亚肌腱钩有啥用 肌腱钩怎么做怎么获得

泰拉瑞亚肌腱钩有啥用 肌腱钩怎么做怎么获得

泰拉瑞亚反重力钩怎么获得怎么合成 反重力钩怎么用

泰拉瑞亚反重力钩怎么获得怎么合成 反重力钩怎么用

泰拉瑞亚阴森钩爪有什么用 阴森钩爪怎么合成怎么获得

泰拉瑞亚阴森钩爪有什么用 阴森钩爪怎么合成怎么获得

泰拉瑞亚圣诞钩爪有什么用 圣诞钩爪怎么合成怎么获得

泰拉瑞亚圣诞钩爪有什么用 圣诞钩爪怎么合成怎么获得

泰拉瑞亚月钩有什么用 月钩怎么做怎么获得

泰拉瑞亚月钩有什么用 月钩怎么做怎么获得

泰拉瑞亚静止钩有什么用 静止钩怎么获得怎么做

泰拉瑞亚静止钩有什么用 静止钩怎么获得怎么做

泰拉瑞亚蚊子琥珀怎么得 恐龙宝宝掉率概率

泰拉瑞亚蚊子琥珀怎么得 恐龙宝宝掉率概率

泰拉瑞亚吞噬怪骨头有什么用 吞噬怪骨头怎么得

泰拉瑞亚吞噬怪骨头有什么用 吞噬怪骨头怎么得

泰拉瑞亚脸怪宝宝有什么用 骨头拨浪鼓骨头乐怎么获得

泰拉瑞亚脸怪宝宝有什么用 骨头拨浪鼓骨头乐怎么获得

泰拉瑞亚格林奇宝宝有什么用 格林奇宝宝的恶作剧口哨怎么获得

泰拉瑞亚格林奇宝宝有什么用 格林奇宝宝的恶作剧口哨怎么获得

泰拉瑞亚花蜜怎么获得 黄蜂宝宝有什么用

泰拉瑞亚花蜜怎么获得 黄蜂宝宝有什么用

泰拉瑞亚地狱蛋糕块有什么用 小鬼宝宝怎么长大

泰拉瑞亚地狱蛋糕块有什么用 小鬼宝宝怎么长大

泰拉瑞亚鱼怎么获得 企鹅宝宝有什么用

泰拉瑞亚鱼怎么获得 企鹅宝宝有什么用

泰拉瑞亚竹叶怎么获得 小熊猫宝宝有什么用

泰拉瑞亚竹叶怎么获得 小熊猫宝宝有什么用

泰拉瑞亚骷髅王头宝宝有什么用 骨头钥匙怎么获得

泰拉瑞亚骷髅王头宝宝有什么用 骨头钥匙怎么获得

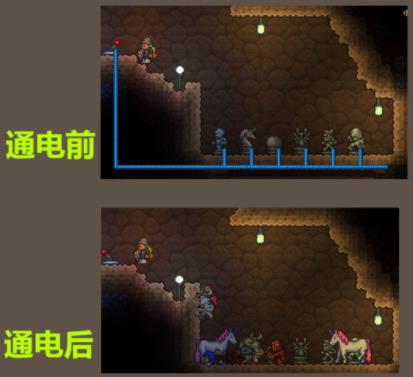

解决非酋的烦恼:泰拉瑞亚刷材料攻略 刷物品装置怎么做

解决非酋的烦恼:泰拉瑞亚刷材料攻略 刷物品装置怎么做

泰拉瑞亚玩具雪橇怎么获得 雪人宝宝有什么用

泰拉瑞亚玩具雪橇怎么获得 雪人宝宝有什么用

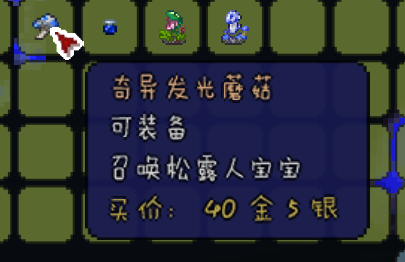

泰拉瑞亚松露人宝宝有什么用 奇异发光蘑菇怎么获得

泰拉瑞亚松露人宝宝有什么用 奇异发光蘑菇怎么获得

泰拉瑞亚狼人宝宝有什么用 满月尖叫玩具怎么获得

泰拉瑞亚狼人宝宝有什么用 满月尖叫玩具怎么获得

泰拉瑞亚黑猫宠物怎么获得 霉运纱线怎么获得

泰拉瑞亚黑猫宠物怎么获得 霉运纱线怎么获得

泰拉瑞亚胡萝卜怎么获得 宠物兔兔有什么用

泰拉瑞亚胡萝卜怎么获得 宠物兔兔有什么用

泰拉瑞亚灾厄mod 灾厄史莱姆之神怎么召唤怎么打

泰拉瑞亚灾厄mod 灾厄史莱姆之神怎么召唤怎么打

泰拉瑞亚同伴方块有什么用彩蛋 同伴方块怎么获得

泰拉瑞亚同伴方块有什么用彩蛋 同伴方块怎么获得

泰拉瑞亚诅咒树苗怎么获得 诅咒树苗有什么用

泰拉瑞亚诅咒树苗怎么获得 诅咒树苗有什么用

泰拉瑞亚雷管小猫有什么用 保险丝球怎么获得

泰拉瑞亚雷管小猫有什么用 保险丝球怎么获得

泰拉瑞亚天界魔棒(天神权杖)怎么获得 埃斯蒂有什么用

泰拉瑞亚天界魔棒(天神权杖)怎么获得 埃斯蒂有什么用

泰拉瑞亚弹簧眼怎么获得 弹簧眼有什么用

泰拉瑞亚弹簧眼怎么获得 弹簧眼有什么用

泰拉瑞亚耳廓狐宠物有什么用 奇异咀嚼玩具怎么获得

泰拉瑞亚耳廓狐宠物有什么用 奇异咀嚼玩具怎么获得

泰拉瑞亚鞋带束头怎么获得 金属带扣有什么用

泰拉瑞亚鞋带束头怎么获得 金属带扣有什么用

泰拉瑞亚疾风脚镯怎么获得 疾风脚镯可以合成什么

泰拉瑞亚疾风脚镯怎么获得 疾风脚镯可以合成什么

泰拉瑞亚水陆两用靴有什么用 水陆两用靴怎么获得

泰拉瑞亚水陆两用靴有什么用 水陆两用靴怎么获得

泰拉瑞亚沙丘行者靴怎样获得 沙丘行者靴有什么用

泰拉瑞亚沙丘行者靴怎样获得 沙丘行者靴有什么用

泰拉瑞亚仙灵靴可以合成什么 仙灵靴怎么获得

泰拉瑞亚仙灵靴可以合成什么 仙灵靴怎么获得

泰拉瑞亚疾风雪靴怎么获得 疾风雪靴可以合成什么

泰拉瑞亚疾风雪靴怎么获得 疾风雪靴可以合成什么

泰拉瑞亚霜花靴有什么用 霜花靴还能合成什么

泰拉瑞亚霜花靴有什么用 霜花靴还能合成什么

泰拉瑞亚赫尔墨斯靴可以合成什么 赫尔墨斯靴怎么获得

泰拉瑞亚赫尔墨斯靴可以合成什么 赫尔墨斯靴怎么获得

泰拉瑞亚闪电靴能合成什么 闪电靴怎么做

泰拉瑞亚闪电靴能合成什么 闪电靴怎么做

泰拉瑞亚航鱼靴怎么做 航鱼靴可以合成什么

泰拉瑞亚航鱼靴怎么做 航鱼靴可以合成什么

泰拉瑞亚闪光蝴蝶眩怎么获得 眩晕花蜜召唤的蝴蝶有什么用

泰拉瑞亚闪光蝴蝶眩怎么获得 眩晕花蜜召唤的蝴蝶有什么用

泰拉瑞亚幽灵靴能合成什么 幽灵靴怎么获得

泰拉瑞亚幽灵靴能合成什么 幽灵靴怎么获得

泰拉瑞亚分趾厚底袜怎么获得 分趾厚底袜可以合成什么

泰拉瑞亚分趾厚底袜怎么获得 分趾厚底袜可以合成什么

泰拉瑞亚泰拉闪耀靴有什么用 泰拉闪耀靴怎么合成

泰拉瑞亚泰拉闪耀靴有什么用 泰拉闪耀靴怎么合成

泰拉瑞亚恐慌项链有什么用 恐慌项链怎么合成

泰拉瑞亚恐慌项链有什么用 恐慌项链怎么合成

泰拉瑞亚琥珀马掌气球怎么获得 琥珀马掌气球有什么用

泰拉瑞亚琥珀马掌气球怎么获得 琥珀马掌气球有什么用

泰拉瑞亚气球河豚鱼怎么获得 气球河豚鱼可以合成什么

泰拉瑞亚气球河豚鱼怎么获得 气球河豚鱼可以合成什么

泰拉瑞亚暴雪气球有什么用 暴雪气球怎么获得

泰拉瑞亚暴雪气球有什么用 暴雪气球怎么获得

泰拉瑞亚蓝马掌气球有什么用 蓝马掌气球怎么获得

泰拉瑞亚蓝马掌气球有什么用 蓝马掌气球怎么获得

泰拉瑞亚气球束怎么获得 气球束有什么用

泰拉瑞亚气球束怎么获得 气球束有什么用

泰拉瑞亚云朵气球在哪合成 云朵气球可以合成什么

泰拉瑞亚云朵气球在哪合成 云朵气球可以合成什么

泰拉瑞亚臭屁气球怎么得 臭屁气球能合成什么

泰拉瑞亚臭屁气球怎么得 臭屁气球能合成什么

泰拉瑞亚气球束和马掌气球哪个好 绿马掌气球有什么用

泰拉瑞亚气球束和马掌气球哪个好 绿马掌气球有什么用

泰拉瑞亚龙蛋怎么获得 hoardagron有什么用

泰拉瑞亚龙蛋怎么获得 hoardagron有什么用

泰拉瑞亚小鸟拨浪鼓怎么获得 小鸟妖有什么用

泰拉瑞亚小鸟拨浪鼓怎么获得 小鸟妖有什么用

泰拉瑞亚蜥蜴有什么用 蜥蜴蛋怎么获得

泰拉瑞亚蜥蜴有什么用 蜥蜴蛋怎么获得

泰拉瑞亚迷你牛头怪有什么用 塔塔酱怎么获得

泰拉瑞亚迷你牛头怪有什么用 塔塔酱怎么获得

泰拉瑞亚鹦鹉有什么用 鹦鹉饼干怎么获得

泰拉瑞亚鹦鹉有什么用 鹦鹉饼干怎么获得

泰拉瑞亚微型世纪之花有什么用 泥芽怎么获得

泰拉瑞亚微型世纪之花有什么用 泥芽怎么获得

泰拉瑞亚Gato蛋怎么获得 飞翔Gato有什么用

泰拉瑞亚Gato蛋怎么获得 飞翔Gato有什么用

泰拉瑞亚小狗有什么用 狗哨怎么获得

泰拉瑞亚小狗有什么用 狗哨怎么获得

泰拉瑞亚幼苗怎么获得 树苗有什么用

泰拉瑞亚幼苗怎么获得 树苗有什么用

泰拉瑞亚1.4快速通关攻略

泰拉瑞亚1.4快速通关攻略

泰拉瑞亚蜂蜜气球怎么获得 蜂蜜气球有什么用

泰拉瑞亚蜂蜜气球怎么获得 蜂蜜气球有什么用

泰拉瑞亚蜘蛛怎么找 蜘蛛卵怎么得

泰拉瑞亚蜘蛛怎么找 蜘蛛卵怎么得

泰拉瑞亚暗影宝箱怪有什么用 华丽暗影钥匙怎么获得

泰拉瑞亚暗影宝箱怪有什么用 华丽暗影钥匙怎么获得

泰拉瑞亚小鲨鱼宠物有什么用 鲨鱼鱼饵怎么获得

泰拉瑞亚小鲨鱼宠物有什么用 鲨鱼鱼饵怎么获得

泰拉瑞亚南瓜娃娃怎么召唤 魔法南瓜子怎么获得

泰拉瑞亚南瓜娃娃怎么召唤 魔法南瓜子怎么获得

泰拉瑞亚蜜袋鼬有什么用 桉树汁怎么刷掉率

泰拉瑞亚蜜袋鼬有什么用 桉树汁怎么刷掉率

泰拉瑞亚提基幽魂有什么用 提基图腾怎么获得

泰拉瑞亚提基幽魂有什么用 提基图腾怎么获得

泰拉瑞亚龟有什么用 海草怎么召唤海龟

泰拉瑞亚龟有什么用 海草怎么召唤海龟

泰拉瑞亚伏特兔怎么获得 闪电胡萝卜怎么得

泰拉瑞亚伏特兔怎么获得 闪电胡萝卜怎么得

泰拉瑞亚和风鱼有什么用 和风鱼掉率是多少

泰拉瑞亚和风鱼有什么用 和风鱼掉率是多少

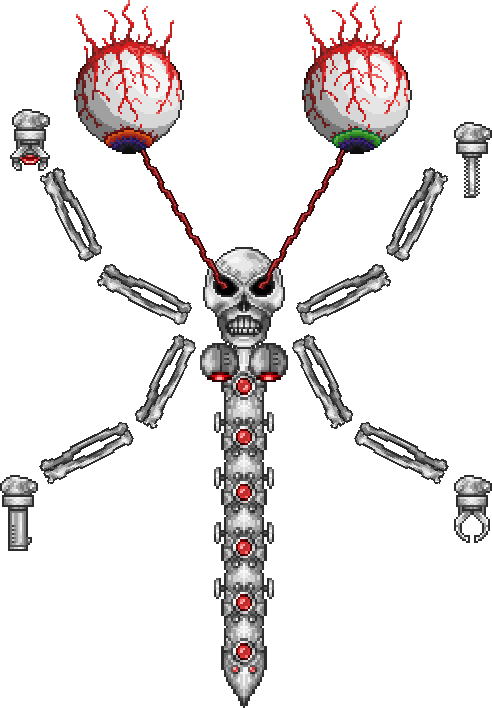

泰拉瑞亚机械毁灭者掉落物 失效探测器怎么获得

泰拉瑞亚机械毁灭者掉落物 失效探测器怎么获得

泰拉瑞亚宇宙滑板有什么用 异星滑板小子怎么获得

泰拉瑞亚宇宙滑板有什么用 异星滑板小子怎么获得

泰拉瑞亚食人魔宝宝在哪 食人魔棍棒怎么获得

泰拉瑞亚食人魔宝宝在哪 食人魔棍棒怎么获得

泰拉瑞亚蠕虫吞噬怪怎么获得 蠕动残骸有什么用

泰拉瑞亚蠕虫吞噬怪怎么获得 蠕动残骸有什么用

泰拉瑞亚常绿尖叫怪树苗有什么用 灌木星星怎么获得

泰拉瑞亚常绿尖叫怪树苗有什么用 灌木星星怎么获得

泰拉瑞亚电线怎么合成有什么用 电线怎么拆怎么放

泰拉瑞亚电线怎么合成有什么用 电线怎么拆怎么放

泰拉瑞亚扳手怎么做有什么用 扳手合成表分享

泰拉瑞亚扳手怎么做有什么用 扳手合成表分享

泰拉瑞亚钢丝钳怎么合成有什么用 钢丝钳合成方式分享

泰拉瑞亚钢丝钳怎么合成有什么用 钢丝钳合成方式分享

泰拉瑞亚五彩扳手怎么获得怎么用 五彩扳手合成图分享

泰拉瑞亚五彩扳手怎么获得怎么用 五彩扳手合成图分享

泰拉瑞亚宏伟蓝图怎么合成怎么用 宏伟蓝图配方分享

泰拉瑞亚宏伟蓝图怎么合成怎么用 宏伟蓝图配方分享

泰拉瑞亚制动魔杖怎么得怎么用 致动魔杖有什么用

泰拉瑞亚制动魔杖怎么得怎么用 致动魔杖有什么用

泰拉瑞亚机械晶状体有什么用怎么得 机械晶状体合成表

泰拉瑞亚机械晶状体有什么用怎么得 机械晶状体合成表

泰拉瑞亚自动安放器有什么用 自动安放器可以干嘛

泰拉瑞亚自动安放器有什么用 自动安放器可以干嘛

泰拉瑞亚粉马掌气球怎么获得 粉马蹄气球有什么用

泰拉瑞亚粉马掌气球怎么获得 粉马蹄气球有什么用

泰拉瑞亚沙暴气球怎么获得 沙暴气球有什么用

泰拉瑞亚沙暴气球怎么获得 沙暴气球有什么用

泰拉瑞亚控制杆怎么用怎么做 控制杆和开关的区别

泰拉瑞亚控制杆怎么用怎么做 控制杆和开关的区别

泰拉瑞亚开关怎么做怎么用 开关怎么合成

泰拉瑞亚开关怎么做怎么用 开关怎么合成

泰拉瑞亚鲨鱼龙气球怎么获得 鲨鱼龙气球可以合成什么

泰拉瑞亚鲨鱼龙气球怎么获得 鲨鱼龙气球可以合成什么

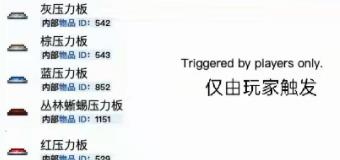

泰拉瑞亚压力板怎么做怎么用 压力板在哪合成

泰拉瑞亚压力板怎么做怎么用 压力板在哪合成

泰拉瑞亚远古号角如何获取 远古号角怎么使用

泰拉瑞亚远古号角如何获取 远古号角怎么使用

泰拉瑞亚黑铆钉鞍有什么用 黑马坐骑介绍

泰拉瑞亚黑铆钉鞍有什么用 黑马坐骑介绍

泰拉瑞亚独角兽坐骑怎么召唤 恩赐苹果有什么用

泰拉瑞亚独角兽坐骑怎么召唤 恩赐苹果有什么用

泰拉瑞亚扰脑器有什么用 扰脑器怎么获得

泰拉瑞亚扰脑器有什么用 扰脑器怎么获得

泰拉瑞亚宇宙车钥匙怎么获得 宇宙车钥匙掉落几率

泰拉瑞亚宇宙车钥匙怎么获得 宇宙车钥匙掉落几率

泰拉瑞亚暗黑魔法师巨著怎么使用 书座骑怎么召唤

泰拉瑞亚暗黑魔法师巨著怎么使用 书座骑怎么召唤

泰拉瑞亚钻头控制装置怎么合成 钻头控制装置有什么用

泰拉瑞亚钻头控制装置怎么合成 钻头控制装置有什么用

泰拉瑞亚中皇家鎏金鞍有什么用 骏马坐骑实用性分享

泰拉瑞亚中皇家鎏金鞍有什么用 骏马坐骑实用性分享

泰拉瑞亚中蒙尘牛皮鞍获取方法 花马坐骑能力测评

泰拉瑞亚中蒙尘牛皮鞍获取方法 花马坐骑能力测评

泰拉瑞亚计时器哪里买 计时器有什么用

泰拉瑞亚计时器哪里买 计时器有什么用

泰拉瑞亚引爆器怎么引爆 引爆器怎么用

泰拉瑞亚引爆器怎么引爆 引爆器怎么用

泰拉瑞亚机关宝箱怎么开 机关宝箱在哪里

泰拉瑞亚机关宝箱怎么开 机关宝箱在哪里

泰拉瑞亚宝石锁有什么用 宝石锁怎么合成

泰拉瑞亚宝石锁有什么用 宝石锁怎么合成

泰拉瑞亚高尔夫球洞在哪 高尔夫球洞怎么玩

泰拉瑞亚高尔夫球洞在哪 高尔夫球洞怎么玩

泰拉瑞亚通电石块怎么用 通电石块怎么获得

泰拉瑞亚通电石块怎么用 通电石块怎么获得

泰拉瑞亚致动器怎么拆 致动器有什么用

泰拉瑞亚致动器怎么拆 致动器有什么用

泰拉瑞亚广播盒怎么用怎么做 广播盒怎么改颜色

泰拉瑞亚广播盒怎么用怎么做 广播盒怎么改颜色

泰拉瑞亚水泵怎么用怎么合成 水泵在哪里买

泰拉瑞亚水泵怎么用怎么合成 水泵在哪里买

泰拉瑞亚格栅怎么用 格栅怎么做

泰拉瑞亚格栅怎么用 格栅怎么做

泰拉瑞亚闪亮红气球怎么获得 闪亮红气球合成什么好

泰拉瑞亚闪亮红气球怎么获得 闪亮红气球合成什么好

泰拉瑞亚传送机器怎么用 传送机器怎么启动

泰拉瑞亚传送机器怎么用 传送机器怎么启动

泰拉瑞亚白马掌气球可以合成什么 白马掌气球获取方式分享

泰拉瑞亚白马掌气球可以合成什么 白马掌气球获取方式分享

泰拉瑞亚黄马掌气球怎么获得 黄马掌气球和绿马蹄那个好

泰拉瑞亚黄马掌气球怎么获得 黄马掌气球和绿马蹄那个好

泰拉瑞亚暴雪瓶可以合成什么 暴雪瓶有什么用怎么获得

泰拉瑞亚暴雪瓶可以合成什么 暴雪瓶有什么用怎么获得

泰拉瑞亚云朵瓶怎么获得 云朵瓶合成表

泰拉瑞亚云朵瓶怎么获得 云朵瓶合成表

泰拉瑞亚晶莹宝石块怎么做 晶莹宝石块有什么用

泰拉瑞亚晶莹宝石块怎么做 晶莹宝石块有什么用

泰拉瑞亚飞镖机关怎么使用 飞镖机关怎么合成和触发

泰拉瑞亚飞镖机关怎么使用 飞镖机关怎么合成和触发

泰拉瑞亚超级飞镖机关怎么做 超级飞镖机关对怪有伤害吗

泰拉瑞亚超级飞镖机关怎么做 超级飞镖机关对怪有伤害吗

泰拉瑞亚长矛机关怎么改变方向 长矛机关怎么用怎么做

泰拉瑞亚长矛机关怎么改变方向 长矛机关怎么用怎么做

泰拉瑞亚尖球机关怎么做有什么用 尖球机关最多放几个

泰拉瑞亚尖球机关怎么做有什么用 尖球机关最多放几个

泰拉瑞亚绒毛胡萝卜怎么召唤 绒毛胡萝卜怎么获得

泰拉瑞亚绒毛胡萝卜怎么召唤 绒毛胡萝卜怎么获得

泰拉瑞亚明胶女式鞍怎么获得 羽翼史莱姆怎么获得

泰拉瑞亚明胶女式鞍怎么获得 羽翼史莱姆怎么获得

泰拉瑞亚山羊骷髅头怎么获得 肉山坐骑掉率怎么样

泰拉瑞亚山羊骷髅头怎么获得 肉山坐骑掉率怎么样

泰拉瑞亚高尔夫球车钥匙获得 高尔夫球车钥匙获取攻略

泰拉瑞亚高尔夫球车钥匙获得 高尔夫球车钥匙获取攻略

泰拉瑞亚硬鞍有什么用 硬鞍怎么获得

泰拉瑞亚硬鞍有什么用 硬鞍怎么获得

泰拉瑞亚魔法树枝怎么获得 魔法树枝有什么用

泰拉瑞亚魔法树枝怎么获得 魔法树枝有什么用

泰拉瑞亚涂蜜护目镜怎么用 蜂王坐骑掉率怎么样

泰拉瑞亚涂蜜护目镜怎么用 蜂王坐骑掉率怎么样

泰拉瑞亚贝壳哨(软体动物口哨)有什么用 火烈鸟坐骑怎么获得

泰拉瑞亚贝壳哨(软体动物口哨)有什么用 火烈鸟坐骑怎么获得

泰拉瑞亚蹦蹦跷怎么用 蹦蹦跷解锁方式

泰拉瑞亚蹦蹦跷怎么用 蹦蹦跷解锁方式

泰拉瑞亚驯鹿铃铛怎么得 冰雪女王坐骑掉率怎么样

泰拉瑞亚驯鹿铃铛怎么得 冰雪女王坐骑掉率怎么样

泰拉瑞亚带鳞松露怎么钓 带鳞松露有什么用

泰拉瑞亚带鳞松露怎么钓 带鳞松露有什么用

泰拉瑞亚虾松露怎么获得 虾松露怎么用

泰拉瑞亚虾松露怎么获得 虾松露怎么用

泰拉瑞亚粘鞍怎么过的 粘鞍怎么召唤

泰拉瑞亚粘鞍怎么过的 粘鞍怎么召唤

泰拉瑞亚过热的血座骑怎么样 获得过热的血的概率

泰拉瑞亚过热的血座骑怎么样 获得过热的血的概率

泰拉瑞亚黑斑怎么获得怎么加速 黑卷坐骑速度怎么样

泰拉瑞亚黑斑怎么获得怎么加速 黑卷坐骑速度怎么样

泰拉瑞亚玩具坦克怎么获得 霜月坦克怎么召唤

泰拉瑞亚玩具坦克怎么获得 霜月坦克怎么召唤

泰拉瑞亚女巫扫帚怎么获得 女巫扫帚怎么使用

泰拉瑞亚女巫扫帚怎么获得 女巫扫帚怎么使用

泰拉瑞亚罐中臭屁可以合成什么 罐中臭屁怎么合成

泰拉瑞亚罐中臭屁可以合成什么 罐中臭屁怎么合成

泰拉瑞亚沙暴瓶怎么获得 沙暴瓶有什么用

泰拉瑞亚沙暴瓶怎么获得 沙暴瓶有什么用

泰拉瑞亚海啸瓶怎么获得 海啸瓶可以合成什么

泰拉瑞亚海啸瓶怎么获得 海啸瓶可以合成什么

泰拉瑞亚烈焰机关怎么获得怎么用 烈焰机关怎么换方向

泰拉瑞亚烈焰机关怎么获得怎么用 烈焰机关怎么换方向

泰拉瑞亚炸药有哪些 炸药怎么合成

泰拉瑞亚炸药有哪些 炸药怎么合成

泰拉瑞亚热喷泉是什么 热喷泉有什么用

泰拉瑞亚热喷泉是什么 热喷泉有什么用

泰拉瑞亚蛙腿怎么快速获得 蛙腿合成什么最好

泰拉瑞亚蛙腿怎么快速获得 蛙腿合成什么最好

泰拉瑞亚铜表在哪里做 铜表和金表有什么区别

泰拉瑞亚铜表在哪里做 铜表和金表有什么区别

泰拉瑞亚翱翔徽章怎么获得 翱翔徽章怎么用

泰拉瑞亚翱翔徽章怎么获得 翱翔徽章怎么用

泰拉瑞亚锡表在哪里合成 锡表怎么做

泰拉瑞亚锡表在哪里合成 锡表怎么做

泰拉瑞亚银表怎么做在哪里制作 银表可以合成什么

泰拉瑞亚银表怎么做在哪里制作 银表可以合成什么

泰拉瑞亚悬浮板怎么做 泰拉瑞亚悬浮板怎么停

泰拉瑞亚悬浮板怎么做 泰拉瑞亚悬浮板怎么停

泰拉瑞亚钨表在哪里合成 钨表有什么用

泰拉瑞亚钨表在哪里合成 钨表有什么用

泰拉瑞亚金表怎么做在哪里合成 金表可以合成什么

泰拉瑞亚金表怎么做在哪里合成 金表可以合成什么

泰拉瑞亚铂金表怎么制作 铂金表在哪里做

泰拉瑞亚铂金表怎么制作 铂金表在哪里做

泰拉瑞亚罗盘在哪里刷 罗盘可以合成什么

泰拉瑞亚罗盘在哪里刷 罗盘可以合成什么

泰拉瑞亚深度计怎么合成 深度计有什么用

泰拉瑞亚深度计怎么合成 深度计有什么用

泰拉瑞亚全球定位系统怎么合成 全球定位系统有什么用

泰拉瑞亚全球定位系统怎么合成 全球定位系统有什么用

泰拉瑞亚渔民袖珍宝典怎么用怎么获得 渔民袖珍宝典显示警告怎么办

泰拉瑞亚渔民袖珍宝典怎么用怎么获得 渔民袖珍宝典显示警告怎么办

泰拉瑞亚天气收音机怎么得有什么用 天气收音机需要多少次

泰拉瑞亚天气收音机怎么得有什么用 天气收音机需要多少次

泰拉瑞亚六分仪怎么获得 六分仪有什么用

泰拉瑞亚六分仪怎么获得 六分仪有什么用

泰拉瑞亚探鱼器怎么做 探鱼器有什么用

泰拉瑞亚探鱼器怎么做 探鱼器有什么用

泰拉瑞亚金属探测器怎么得 金属探测器怎么用

泰拉瑞亚金属探测器怎么得 金属探测器怎么用

泰拉瑞亚秒表怎么快速获得有什么用 秒表可以合成什么

泰拉瑞亚秒表怎么快速获得有什么用 秒表可以合成什么

泰拉瑞亚每秒伤害计数器哪里得 每秒伤害计数器合成什么

泰拉瑞亚每秒伤害计数器哪里得 每秒伤害计数器合成什么

泰拉瑞亚哥布林数据仪怎么合成 哥布林数据仪有什么用

泰拉瑞亚哥布林数据仪怎么合成 哥布林数据仪有什么用

泰拉瑞亚天界星盘怎么获得 天界星盘怎么悬浮

泰拉瑞亚天界星盘怎么获得 天界星盘怎么悬浮

泰拉瑞亚北极潜水装置怎么获得 北极潜水装置有用吗

泰拉瑞亚北极潜水装置怎么获得 北极潜水装置有用吗

泰拉瑞亚杀怪计数器怎么获得 杀怪计数器可以合成什么

泰拉瑞亚杀怪计数器怎么获得 杀怪计数器可以合成什么

泰拉瑞亚潜水装备wiki 潜水装置怎么获得

泰拉瑞亚潜水装备wiki 潜水装置怎么获得

泰拉瑞亚生命体分析仪如何获得怎么用 生命体分析仪能合成什么

泰拉瑞亚生命体分析仪如何获得怎么用 生命体分析仪能合成什么

泰拉瑞亚浮游圈合成 浮游圈怎么获得

泰拉瑞亚浮游圈合成 浮游圈怎么获得

泰拉瑞亚脚蹼在哪里 脚蹼能合成什么

泰拉瑞亚脚蹼在哪里 脚蹼能合成什么

泰拉瑞亚雷达怎么快速获得有什么用 雷达可以和什么合成

泰拉瑞亚雷达怎么快速获得有什么用 雷达可以和什么合成

泰拉瑞亚R.E.K.3000有什么用 R.E.K.3000怎么做

泰拉瑞亚R.E.K.3000有什么用 R.E.K.3000怎么做

泰拉瑞亚青蛙脚蹼可以合成什么 青蛙脚蹼有什么用

泰拉瑞亚青蛙脚蹼可以合成什么 青蛙脚蹼有什么用

泰拉瑞亚个人数字助手怎么获得 个人数字助手可以合成什么

泰拉瑞亚个人数字助手怎么获得 个人数字助手可以合成什么

泰拉瑞亚标尺怎么得怎么用 标尺怎么打开怎么关掉

泰拉瑞亚标尺怎么得怎么用 标尺怎么打开怎么关掉

泰拉瑞亚水母潜水装备合成 水母潜水装备怎么获得

泰拉瑞亚水母潜水装备合成 水母潜水装备怎么获得

泰拉瑞亚机械标尺合成有什么用 机械标尺怎么关闭测量线

泰拉瑞亚机械标尺合成有什么用 机械标尺怎么关闭测量线

泰拉瑞亚远古凿子有什么用 远古凿子怎么获得

泰拉瑞亚远古凿子有什么用 远古凿子怎么获得

泰拉瑞亚加长握爪能合成什么 加长握爪怎么获得有什么用

泰拉瑞亚加长握爪能合成什么 加长握爪怎么获得有什么用

泰拉瑞亚工具腰带有什么用 工具腰带怎么得

泰拉瑞亚工具腰带有什么用 工具腰带怎么得

泰拉瑞亚工具箱怎么获得 工具箱怎么用

泰拉瑞亚工具箱怎么获得 工具箱怎么用

泰拉瑞亚砌砖刀有什么用 砌砖刀怎么获得

泰拉瑞亚砌砖刀有什么用 砌砖刀怎么获得

泰拉瑞亚便携式水泥搅拌机怎么获得 便携式水泥搅拌机有什么用

泰拉瑞亚便携式水泥搅拌机怎么获得 便携式水泥搅拌机有什么用

泰拉瑞亚喷漆器怎么用怎么获得 喷漆器可以合成什么

泰拉瑞亚喷漆器怎么用怎么获得 喷漆器可以合成什么

泰拉瑞亚建筑师发明背包怎么获得 建筑师发明背包怎么用

泰拉瑞亚建筑师发明背包怎么获得 建筑师发明背包怎么用

泰拉瑞亚暗影珠有什么用 暗影珠在哪里找

泰拉瑞亚暗影珠有什么用 暗影珠在哪里找

泰拉瑞亚自动安放器有什么用怎么获得 自动安放器怎么使用

泰拉瑞亚自动安放器有什么用怎么获得 自动安放器怎么使用

泰拉瑞亚仙灵铃铛怎么召唤 仙灵铃铛在哪合成

泰拉瑞亚仙灵铃铛怎么召唤 仙灵铃铛在哪合成

泰拉瑞亚飞眼怪蛋怎么获得 飞眼怪蛋怎么召唤

泰拉瑞亚飞眼怪蛋怎么获得 飞眼怪蛋怎么召唤

泰拉瑞亚石巨人守卫怎么获得 石巨人宠物掉率怎么样

泰拉瑞亚石巨人守卫怎么获得 石巨人宠物掉率怎么样

泰拉瑞亚光之珠宝怎么得 光之女皇宠物掉率怎么样

泰拉瑞亚光之珠宝怎么得 光之女皇宠物掉率怎么样

泰拉瑞亚南瓜香薰蜡烛怎么获得 南瓜香薰蜡烛几率怎么样

泰拉瑞亚南瓜香薰蜡烛怎么获得 南瓜香薰蜡烛几率怎么样

泰拉瑞亚妖灵瓶如何获得 妖灵瓶掉率怎么样

泰拉瑞亚妖灵瓶如何获得 妖灵瓶掉率怎么样

泰拉瑞亚可疑触手怎么获得 月亮领主掉落可疑触手吗

泰拉瑞亚可疑触手怎么获得 月亮领主掉落可疑触手吗

泰拉瑞亚双筒望远镜怎么获得 双筒望远镜专家模式爆率怎么样

泰拉瑞亚双筒望远镜怎么获得 双筒望远镜专家模式爆率怎么样

泰拉瑞亚幽灵护目镜有什么用 幽灵护目镜怎么获得

泰拉瑞亚幽灵护目镜有什么用 幽灵护目镜怎么获得

泰拉瑞亚渔夫耳环怎么得有什么用 渔夫耳环能不能叠加

泰拉瑞亚渔夫耳环怎么得有什么用 渔夫耳环能不能叠加

泰拉瑞亚优质钓鱼线可以合成什么 优质钓鱼线怎么获得有什么用

泰拉瑞亚优质钓鱼线可以合成什么 优质钓鱼线怎么获得有什么用

泰拉瑞亚芦苇呼吸管怎么合成 芦苇呼吸管怎么使用

泰拉瑞亚芦苇呼吸管怎么合成 芦苇呼吸管怎么使用

泰拉瑞亚魔镜怎么合成 魔镜在哪里找

泰拉瑞亚魔镜怎么合成 魔镜在哪里找

泰拉瑞亚渔夫渔具袋怎么获得可以合成什么 渔夫渔具袋不装备有效果么

泰拉瑞亚渔夫渔具袋怎么获得可以合成什么 渔夫渔具袋不装备有效果么

泰拉瑞亚冰雪镜有什么用 冰雪镜可以合成什么

泰拉瑞亚冰雪镜有什么用 冰雪镜可以合成什么

泰拉瑞亚防熔岩钓钩怎么获得 防熔岩钓钩有什么用

泰拉瑞亚防熔岩钓钩怎么获得 防熔岩钓钩有什么用

泰拉瑞亚防熔岩渔具袋怎么获得 防熔岩渔具袋有什么用

泰拉瑞亚防熔岩渔具袋怎么获得 防熔岩渔具袋有什么用

泰拉瑞亚向导巫毒娃娃怎么获得怎么用 向导巫毒娃娃怎么扔

泰拉瑞亚向导巫毒娃娃怎么获得怎么用 向导巫毒娃娃怎么扔

泰拉瑞亚服装商巫毒娃娃有什么用怎么获得 服装商巫毒娃娃怎么使用

泰拉瑞亚服装商巫毒娃娃有什么用怎么获得 服装商巫毒娃娃怎么使用

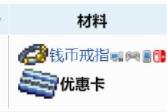

泰拉瑞亚钱币戒指怎么获得 钱币戒指有什么用

泰拉瑞亚钱币戒指怎么获得 钱币戒指有什么用

泰拉瑞亚优惠卡怎么得有什么用 优惠卡能组合什么

泰拉瑞亚优惠卡怎么得有什么用 优惠卡能组合什么

泰拉瑞亚烈焰靴有什么用 烈焰靴怎么得

泰拉瑞亚烈焰靴有什么用 烈焰靴怎么得

泰拉瑞亚海神贝壳怎么得 海神贝壳可以合成什么

泰拉瑞亚海神贝壳怎么得 海神贝壳可以合成什么

泰拉瑞亚花靴怎么用怎么做 花靴怎么用可以合成什么

泰拉瑞亚花靴怎么用怎么做 花靴怎么用可以合成什么

泰拉瑞亚金戒指怎么得 金戒指有什么用

泰拉瑞亚金戒指怎么得 金戒指有什么用

泰拉瑞亚水上漂靴怎么获得 水上漂靴合成

泰拉瑞亚水上漂靴怎么获得 水上漂靴合成

泰拉瑞亚黑曜石水上行走靴 黑曜石水上漂靴子有什么用

泰拉瑞亚黑曜石水上行走靴 黑曜石水上漂靴子有什么用

泰拉瑞亚高尔夫球怎么玩 高尔夫球怎么获得

泰拉瑞亚高尔夫球怎么玩 高尔夫球怎么获得

泰拉瑞亚熔岩靴怎么合成 熔岩靴怎么获得

泰拉瑞亚熔岩靴怎么合成 熔岩靴怎么获得

泰拉瑞亚贪婪戒指怎么获得有什么用 贪婪戒指可以合成什么

泰拉瑞亚贪婪戒指怎么获得有什么用 贪婪戒指可以合成什么

泰拉瑞亚植物纤维绳索宝典有什么用 植物纤维绳索宝典如何得到

泰拉瑞亚植物纤维绳索宝典有什么用 植物纤维绳索宝典如何得到

泰拉瑞亚水母项链怎么获得有什么用 水母项链可以合成什么

泰拉瑞亚水母项链怎么获得有什么用 水母项链可以合成什么

泰拉瑞亚幸运币怎么获得 幸运币有什么用

泰拉瑞亚幸运币怎么获得 幸运币有什么用

泰拉瑞亚梯凳有什么用 梯凳可以合成什么

泰拉瑞亚梯凳有什么用 梯凳可以合成什么

泰拉瑞亚宝藏磁石有什么用怎么获得 宝藏磁石可以合成什么

泰拉瑞亚宝藏磁石有什么用怎么获得 宝藏磁石可以合成什么

泰拉瑞亚狂战士手套怎么合成有什么用 狂战士手套怎么自动攻击

泰拉瑞亚狂战士手套怎么合成有什么用 狂战士手套怎么自动攻击

泰拉瑞亚猛爪手套可以合成什么 猛爪手套怎么获得有什么用

泰拉瑞亚猛爪手套可以合成什么 猛爪手套怎么获得有什么用

泰拉瑞亚烈火手套怎么获得有什么用 烈火手套可以合成什么

泰拉瑞亚烈火手套怎么获得有什么用 烈火手套可以合成什么

泰拉瑞亚机械手套怎么获得 机械手套有什么用

泰拉瑞亚机械手套怎么获得 机械手套有什么用

泰拉瑞亚强力手套怎么获得有什么用 强力手套可以合成什么

泰拉瑞亚强力手套怎么获得有什么用 强力手套可以合成什么

泰拉瑞亚泰坦手套怎么获得有什么用 泰坦手套可以合成什么

泰拉瑞亚泰坦手套怎么获得有什么用 泰坦手套可以合成什么

泰拉瑞亚战士徽章怎么获得有什么用 战士徽章可以合成什么

泰拉瑞亚战士徽章怎么获得有什么用 战士徽章可以合成什么

泰拉瑞亚地狱火战靴合成表 狱炎战靴(狱炎花纹)怎么合成

泰拉瑞亚地狱火战靴合成表 狱炎战靴(狱炎花纹)怎么合成

泰拉瑞亚远古套装怎么得? 泰拉瑞亚远古套装属性

泰拉瑞亚远古套装怎么得? 泰拉瑞亚远古套装属性

泰拉瑞亚魔法箭袋怎么获得 魔法箭袋可以合成什么

泰拉瑞亚魔法箭袋怎么获得 魔法箭袋可以合成什么

泰拉瑞亚熔火箭袋怎么获得 熔火箭袋可以合成什么

泰拉瑞亚熔火箭袋怎么获得 熔火箭袋可以合成什么

泰拉瑞亚游侠徽章怎么获得 游侠徽章有什么用

泰拉瑞亚游侠徽章怎么获得 游侠徽章有什么用

泰拉瑞亚侦察镜怎么得 侦察镜有什么用

泰拉瑞亚侦察镜怎么得 侦察镜有什么用

泰拉瑞亚步枪瞄准镜怎么获得 步枪瞄准镜有什么用

泰拉瑞亚步枪瞄准镜怎么获得 步枪瞄准镜有什么用

泰拉瑞亚狙击镜怎么获得有什么用 狙击镜可以合成什么

泰拉瑞亚狙击镜怎么获得有什么用 狙击镜可以合成什么

泰拉瑞亚潜行者箭袋怎么做有什么用 潜行者箭袋和熔火箭袋哪个好

泰拉瑞亚潜行者箭袋怎么做有什么用 潜行者箭袋和熔火箭袋哪个好

泰拉瑞亚天界徽章怎么合成 天界徽章怎么用

泰拉瑞亚天界徽章怎么合成 天界徽章怎么用

泰拉瑞亚巫士徽章怎么合成 巫士徽章有什么用

泰拉瑞亚巫士徽章怎么合成 巫士徽章有什么用

泰拉瑞亚大力士甲虫怎么获得怎么升级 大力士甲虫合还能合成什么

泰拉瑞亚大力士甲虫怎么获得怎么升级 大力士甲虫合还能合成什么

泰拉瑞亚死灵卷轴怎么得有什么用 死灵卷轴可以叠加吗

泰拉瑞亚死灵卷轴怎么得有什么用 死灵卷轴可以叠加吗

泰拉瑞亚甲虫莎草纸怎么获得 甲虫莎草纸在哪里合成

泰拉瑞亚甲虫莎草纸怎么获得 甲虫莎草纸在哪里合成

泰拉瑞亚矮人项链如何获得有什么用 矮人项链可以合成什么

泰拉瑞亚矮人项链如何获得有什么用 矮人项链可以合成什么

泰拉瑞亚召唤师徽章怎么获得有什么用 召唤师徽章什么版本出现

泰拉瑞亚召唤师徽章怎么获得有什么用 召唤师徽章什么版本出现

泰拉瑞亚闪耀蜜蜂怎么获得 闪耀蜜蜂在哪里有

泰拉瑞亚闪耀蜜蜂怎么获得 闪耀蜜蜂在哪里有

泰拉瑞亚学徒围巾怎么得 学徒围巾有什么用

泰拉瑞亚学徒围巾怎么得 学徒围巾有什么用

泰拉瑞亚女猎人圆盾怎么获得有什么用 女猎人圆盾效果

泰拉瑞亚女猎人圆盾怎么获得有什么用 女猎人圆盾效果

泰拉瑞亚武僧腰带怎么获得 和尚腰带有什么用

泰拉瑞亚武僧腰带怎么获得 和尚腰带有什么用

泰拉瑞亚冰冻王冠怎么得 小冰雪女王宠物怎么召唤

泰拉瑞亚冰冻王冠怎么得 小冰雪女王宠物怎么召唤

泰拉瑞亚侍卫护盾哪里搞 侍卫护盾有什么用

泰拉瑞亚侍卫护盾哪里搞 侍卫护盾有什么用

泰拉瑞亚平衡锤有什么用怎么获得 平衡锤可以合成什么

泰拉瑞亚平衡锤有什么用怎么获得 平衡锤可以合成什么

泰拉瑞亚细绳怎么做 细绳怎么用

泰拉瑞亚细绳怎么做 细绳怎么用

泰拉瑞亚悠悠球袋有什么用怎么合成 悠悠球袋可以叠加吗

泰拉瑞亚悠悠球袋有什么用怎么合成 悠悠球袋可以叠加吗

泰拉瑞亚悠悠球手套怎么获得怎么用 悠悠球手套可以合成什么

泰拉瑞亚悠悠球手套怎么获得怎么用 悠悠球手套可以合成什么

泰拉瑞亚传送枪怎么做 传送枪怎么得

泰拉瑞亚传送枪怎么做 传送枪怎么得

泰拉瑞亚复仇者徽章怎么获得有什么用 复仇者徽章可以合成什么

泰拉瑞亚复仇者徽章怎么获得有什么用 复仇者徽章可以合成什么

泰拉瑞亚生命红木魔棒怎么得 生命红木魔棒有什么用法

泰拉瑞亚生命红木魔棒怎么得 生命红木魔棒有什么用法

泰拉瑞亚蜜蜂斗篷有什么用怎么做 蜜蜂斗篷在哪里合成

泰拉瑞亚蜜蜂斗篷有什么用怎么做 蜜蜂斗篷在哪里合成

泰拉瑞亚天界壳怎么做有什么用 天界壳和天界石哪个好

泰拉瑞亚天界壳怎么做有什么用 天界壳和天界石哪个好

泰拉瑞亚天界石怎么得有什么用 天界石和天界壳叠加吗

泰拉瑞亚天界石怎么得有什么用 天界石和天界壳叠加吗

泰拉瑞亚毁灭者徽章怎么获得能做什么 毁灭者徽章和复仇者徽章哪个好

泰拉瑞亚毁灭者徽章怎么获得能做什么 毁灭者徽章和复仇者徽章哪个好

泰拉瑞亚石巨人之眼怎么获得有什么用 石巨人之眼可以合成什么

泰拉瑞亚石巨人之眼怎么获得有什么用 石巨人之眼可以合成什么

泰拉瑞亚树叶魔棒怎么得 树叶魔棒可以放置什么物块

泰拉瑞亚树叶魔棒怎么得 树叶魔棒可以放置什么物块

泰拉瑞亚生命木魔棒有什么用 生命木魔棒怎么得

泰拉瑞亚生命木魔棒有什么用 生命木魔棒怎么得

泰拉瑞亚蜂巢魔棒有什么用 蜂巢魔棒可以放置什么物块

泰拉瑞亚蜂巢魔棒有什么用 蜂巢魔棒可以放置什么物块

泰拉瑞亚白骨魔棒有什么用 白骨魔棒怎么取消

泰拉瑞亚白骨魔棒有什么用 白骨魔棒怎么取消

泰拉瑞亚红木树叶魔棒哪里能得到 红木树叶魔棒怎么用

泰拉瑞亚红木树叶魔棒哪里能得到 红木树叶魔棒怎么用

泰拉瑞亚混沌传送杖怎么获得 混沌传送杖掉率怎么样

泰拉瑞亚混沌传送杖怎么获得 混沌传送杖掉率怎么样

泰拉瑞亚伞的修饰语是什么 开到伞得几率怎么样

泰拉瑞亚伞的修饰语是什么 开到伞得几率怎么样

泰拉瑞亚悲剧伞修饰语是什么 开到悲剧伞得几率怎么样

泰拉瑞亚悲剧伞修饰语是什么 开到悲剧伞得几率怎么样

泰拉瑞亚魔法海螺在什么地方获得 魔法海螺有什么用

泰拉瑞亚魔法海螺在什么地方获得 魔法海螺有什么用

泰拉瑞亚恶魔海螺怎么获得 恶魔海螺有什么用

泰拉瑞亚恶魔海螺怎么获得 恶魔海螺有什么用

泰拉瑞亚无底水桶怎么使用 泰拉瑞亚无底水桶获得方法

泰拉瑞亚无底水桶怎么使用 泰拉瑞亚无底水桶获得方法

泰拉瑞亚土魔杖有什么用 土魔杖怎么用

泰拉瑞亚土魔杖有什么用 土魔杖怎么用

泰拉瑞亚沙堡桶会在哪里出现 沙堡桶怎么用

泰拉瑞亚沙堡桶会在哪里出现 沙堡桶怎么用

泰拉瑞亚再生法杖怎么获得 再生法杖收花有什么效果

泰拉瑞亚再生法杖怎么获得 再生法杖收花有什么效果

泰拉瑞亚环境改造枪怎么获得 环境改造枪如何快速改造地形

泰拉瑞亚环境改造枪怎么获得 环境改造枪如何快速改造地形

泰拉瑞亚割草机有什么用 割草机在哪里能获得

泰拉瑞亚割草机有什么用 割草机在哪里能获得

泰拉瑞亚无底熔岩桶怎么获得 泰拉瑞亚无底熔岩桶有什么作用

泰拉瑞亚无底熔岩桶怎么获得 泰拉瑞亚无底熔岩桶有什么作用

泰拉瑞亚超级吸水棉怎么放水 泰拉瑞亚超吸水海绵怎么获得

泰拉瑞亚超级吸水棉怎么放水 泰拉瑞亚超吸水海绵怎么获得

泰拉瑞亚粘性土炸弹怎么获取 泰拉瑞亚粘性土炸弹有什么用

泰拉瑞亚粘性土炸弹怎么获取 泰拉瑞亚粘性土炸弹有什么用

泰拉瑞亚镰刀怎么获得 泰拉瑞亚镰刀有什么作用

泰拉瑞亚镰刀怎么获得 泰拉瑞亚镰刀有什么作用

泰拉瑞亚泡泡魔棒怎么获得 泡泡魔棒有什么用

泰拉瑞亚泡泡魔棒怎么获得 泡泡魔棒有什么用

泰拉瑞亚钓竿合成大全怎么合成 鱼竿排行榜分享

泰拉瑞亚钓竿合成大全怎么合成 鱼竿排行榜分享

泰拉瑞亚蛇笛怎么获得 蛇笛有什么用

泰拉瑞亚蛇笛怎么获得 蛇笛有什么用

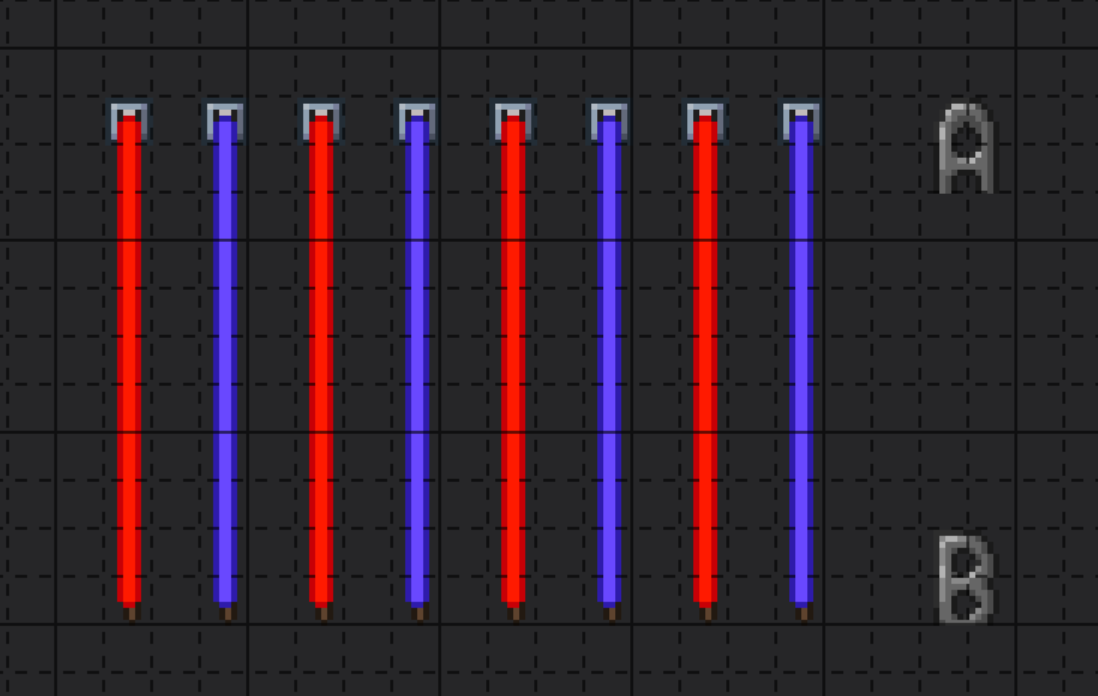

泰拉瑞亚雨之歌怎么获得 泰拉瑞亚雨歌怎么使用

泰拉瑞亚雨之歌怎么获得 泰拉瑞亚雨歌怎么使用

泰拉瑞亚虫网可以合成什么 虫网在哪个商人买

泰拉瑞亚虫网可以合成什么 虫网在哪个商人买

泰拉瑞亚防熔岩虫网有什么用 防熔岩虫网怎么合成

泰拉瑞亚防熔岩虫网有什么用 防熔岩虫网怎么合成

泰拉瑞亚金虫网和熔岩虫网有什么区别 金虫网怎么得

泰拉瑞亚金虫网和熔岩虫网有什么区别 金虫网怎么得

泰拉瑞亚蜂巢背包有什么用怎么得 蜂巢背包对蜜蜂弓有用吗

泰拉瑞亚蜂巢背包有什么用怎么得 蜂巢背包对蜜蜂弓有用吗

泰拉瑞亚蜂窝怎么获得 蜂窝合成什么比较好

泰拉瑞亚蜂窝怎么获得 蜂窝合成什么比较好

泰拉瑞亚岩浆骷髅头可以合成什么 岩浆骷髅头怎么得

泰拉瑞亚岩浆骷髅头可以合成什么 岩浆骷髅头怎么得

泰拉瑞亚岩浆石怎么得可以做什么 岩浆石合成什么好

泰拉瑞亚岩浆石怎么得可以做什么 岩浆石合成什么好

泰拉瑞亚熔火骷髅头玫瑰怎么得 熔火骷髅头玫瑰有什么用

泰拉瑞亚熔火骷髅头玫瑰怎么得 熔火骷髅头玫瑰有什么用

泰拉瑞亚月光护身符如何获得 月光护身符有什么用

泰拉瑞亚月光护身符如何获得 月光护身符有什么用

泰拉瑞亚月亮贝壳有啥用如何获得 月亮贝壳能做什么

泰拉瑞亚月亮贝壳有啥用如何获得 月亮贝壳能做什么

泰拉瑞亚月亮石怎么获得什么用 月亮石能和什么合成

泰拉瑞亚月亮石怎么获得什么用 月亮石能和什么合成

泰拉瑞亚腐香囊怎么获得有什么用 腐香囊可以合成什么

泰拉瑞亚腐香囊怎么获得有什么用 腐香囊可以合成什么

泰拉瑞亚鲨牙项链怎么获得 鲨牙项链好用吗

泰拉瑞亚鲨牙项链怎么获得 鲨牙项链好用吗

泰拉瑞亚克苏鲁护盾可以合成什么 如何使用克苏鲁护盾

泰拉瑞亚克苏鲁护盾可以合成什么 如何使用克苏鲁护盾

泰拉瑞亚孢子囊有什么用怎么获得 孢子囊怎么样

泰拉瑞亚孢子囊有什么用怎么获得 孢子囊怎么样

泰拉瑞亚星星斗篷怎么获得有什么用 星星斗篷合成什么好

泰拉瑞亚星星斗篷怎么获得有什么用 星星斗篷合成什么好

泰拉瑞亚毒刺项链有什么用怎么做 毒刺项链在哪里合成

泰拉瑞亚毒刺项链有什么用怎么做 毒刺项链在哪里合成

泰拉瑞亚太阳石在哪里获得有什么用 太阳石可以合成什么

泰拉瑞亚太阳石在哪里获得有什么用 太阳石可以合成什么

泰拉瑞亚挥发明胶有什么用 挥发明胶怎么获得

泰拉瑞亚挥发明胶有什么用 挥发明胶怎么获得

泰拉瑞亚粘性绷带怎么获得在哪刷 粘性绷带可以合成什么

泰拉瑞亚粘性绷带怎么获得在哪刷 粘性绷带可以合成什么

泰拉瑞亚十字章护身符有什么用怎么得 十字章护身符能合成什么

泰拉瑞亚十字章护身符有什么用怎么得 十字章护身符能合成什么

泰拉瑞亚十字章护盾怎么做有用嘛 十字章护盾可以合成什么

泰拉瑞亚十字章护盾怎么做有用嘛 十字章护盾可以合成什么

泰拉瑞亚盔甲背带怎么获得有什么用 盔甲背带谁掉

泰拉瑞亚盔甲背带怎么获得有什么用 盔甲背带谁掉

泰拉瑞亚盔甲抛光剂怎么获得有什么用 盔甲抛光剂掉的几率是多少

泰拉瑞亚盔甲抛光剂怎么获得有什么用 盔甲抛光剂掉的几率是多少

泰拉瑞亚牛黄怎么获得有什么用 牛黄可以合成什么

泰拉瑞亚牛黄怎么获得有什么用 牛黄可以合成什么

泰拉瑞亚考古学家套装 考古套装怎么获得

泰拉瑞亚考古学家套装 考古套装怎么获得

泰拉瑞亚蒙眼布怎么获得有啥用 蒙眼布可以合成什么

泰拉瑞亚蒙眼布怎么获得有啥用 蒙眼布可以合成什么

泰拉瑞亚反诅咒咒语怎么得 反诅咒咒语有什么用

泰拉瑞亚反诅咒咒语怎么得 反诅咒咒语有什么用

泰拉瑞亚蜜蜂套装怎么获得 蜜蜂套装效果怎么样

泰拉瑞亚蜜蜂套装怎么获得 蜜蜂套装效果怎么样

泰拉瑞亚快走时钟如何获取怎么用 快走时钟在哪刷

泰拉瑞亚快走时钟如何获取怎么用 快走时钟在哪刷

泰拉瑞亚黑毕业套装是哪些 黑毕业套装介绍

泰拉瑞亚黑毕业套装是哪些 黑毕业套装介绍

泰拉瑞亚暖手宝怎么获得 暖手宝哪里打

泰拉瑞亚暖手宝怎么获得 暖手宝哪里打

泰拉瑞亚怎么获得药用绷带 药用绷带有什么用

泰拉瑞亚怎么获得药用绷带 药用绷带有什么用

泰拉瑞亚扩音器怎么得有什么用 扩音器可以合成什么

泰拉瑞亚扩音器怎么得有什么用 扩音器可以合成什么

泰拉瑞亚蓝毕业套装是哪些 蓝毕业套装分享

泰拉瑞亚蓝毕业套装是哪些 蓝毕业套装分享

泰拉瑞亚熔火护身符怎么获得 熔火护身符合成什么

泰拉瑞亚熔火护身符怎么获得 熔火护身符合成什么

泰拉瑞亚褐红毕业套装是哪些 褐红毕业套装获取方式分享

泰拉瑞亚褐红毕业套装是哪些 褐红毕业套装获取方式分享

泰拉瑞亚兔兔套装如何获得 兔兔套装介绍分享

泰拉瑞亚兔兔套装如何获得 兔兔套装介绍分享

泰拉瑞亚邪眼怎么刷 邪眼可以合成什么

泰拉瑞亚邪眼怎么刷 邪眼可以合成什么

泰拉瑞亚黑曜石骷髅头怎么获得有什么用 黑曜石骷髅头免疫岩浆吗

泰拉瑞亚黑曜石骷髅头怎么获得有什么用 黑曜石骷髅头免疫岩浆吗

泰拉瑞亚计划书怎么获得有什么用 计划书可以合成什么

泰拉瑞亚计划书怎么获得有什么用 计划书可以合成什么

泰拉瑞亚三折地图怎么获得怎么刷 三折地图可以合成什么

泰拉瑞亚三折地图怎么获得怎么刷 三折地图可以合成什么

泰拉瑞亚维生素怎么刷 维生素和什么可以合成

泰拉瑞亚维生素怎么刷 维生素和什么可以合成

泰拉瑞亚袖珍镜怎么得有什么用 袖珍镜谁掉

泰拉瑞亚袖珍镜怎么得有什么用 袖珍镜谁掉

泰拉瑞亚黑腰带怎么获得可以合成什么 黑腰带和忍者极意能叠加吗

泰拉瑞亚黑腰带怎么获得可以合成什么 黑腰带和忍者极意能叠加吗

泰拉瑞亚常春藤ivy怎么获得 常春藤ivy会从哪个NPC掉落

泰拉瑞亚常春藤ivy怎么获得 常春藤ivy会从哪个NPC掉落

泰拉瑞亚负重石有什么用 负重石怎么获得

泰拉瑞亚负重石有什么用 负重石怎么获得

泰拉瑞亚灯笼夜是什么 关于灯笼夜的爱心小贴士

泰拉瑞亚灯笼夜是什么 关于灯笼夜的爱心小贴士

泰拉瑞亚小动物友谊指南获得途径 小动物友谊指南怎么使用

泰拉瑞亚小动物友谊指南获得途径 小动物友谊指南怎么使用

泰拉瑞亚流星雨什么时候发生 腥红之地怎么样才会有流星雨

泰拉瑞亚流星雨什么时候发生 腥红之地怎么样才会有流星雨

泰拉瑞亚高尔夫球手在哪 npc高尔夫球手入驻条件及介绍

泰拉瑞亚高尔夫球手在哪 npc高尔夫球手入驻条件及介绍

泰拉瑞亚服装公主有什么用 NPC公主入住条件攻略

泰拉瑞亚服装公主有什么用 NPC公主入住条件攻略

泰拉瑞亚1.4火把神事件是什么 火把神事件介绍

泰拉瑞亚1.4火把神事件是什么 火把神事件介绍

泰拉瑞亚陨石生物群落有什么 陨石生物群落怎么遇见

泰拉瑞亚陨石生物群落有什么 陨石生物群落怎么遇见

泰拉瑞亚篝火能做什么 篝火合成表大全

泰拉瑞亚篝火能做什么 篝火合成表大全

泰拉瑞亚腐变室有什么用 腐变室合成表大全

泰拉瑞亚腐变室有什么用 腐变室合成表大全

泰拉瑞亚裂隙是什么 裂隙通常在哪里可以找到

泰拉瑞亚裂隙是什么 裂隙通常在哪里可以找到

泰拉瑞亚厨师套装怎么获得 厨师套装介绍分享

泰拉瑞亚厨师套装怎么获得 厨师套装介绍分享

泰拉瑞亚小丑套装怎么获得 小丑套装介绍分享

泰拉瑞亚小丑套装怎么获得 小丑套装介绍分享

泰拉瑞亚乡村俱乐部套装怎么获得 乡村俱乐部套装分享

泰拉瑞亚乡村俱乐部套装怎么获得 乡村俱乐部套装分享

泰拉瑞亚牛仔套装怎么得 牛仔套装介绍

泰拉瑞亚牛仔套装怎么得 牛仔套装介绍

泰拉瑞亚邪教徒套装有什么用 邪教徒套装有哪些

泰拉瑞亚邪教徒套装有什么用 邪教徒套装有哪些

泰拉瑞亚狗狗套装如何获得 狗狗套装介绍

泰拉瑞亚狗狗套装如何获得 狗狗套装介绍

泰拉瑞亚混乱之脑怎么获得有什么用 混乱之脑对boss有用吗

泰拉瑞亚混乱之脑怎么获得有什么用 混乱之脑对boss有用吗

泰拉瑞亚便装套装效果 便装套装怎么获得

泰拉瑞亚便装套装效果 便装套装怎么获得

泰拉瑞亚钴护盾怎么做有什么用 钴护盾可以合成什么

泰拉瑞亚钴护盾怎么做有什么用 钴护盾可以合成什么

泰拉瑞亚十字项链怎么刷有什么用 十字项链能合成什么

泰拉瑞亚十字项链怎么刷有什么用 十字项链能合成什么

泰拉瑞亚血肉指虎怎么得 血肉指虎有什么用

泰拉瑞亚血肉指虎怎么得 血肉指虎有什么用

泰拉瑞亚鱼套装有哪些 鱼套装介绍

泰拉瑞亚鱼套装有哪些 鱼套装介绍

泰拉瑞亚冰冻护盾怎么做 冰冻护盾和英雄护盾哪个好

泰拉瑞亚冰冻护盾怎么做 冰冻护盾和英雄护盾哪个好

泰拉瑞亚狐狸套装(动物学家)怎么得 狐狸套装获取攻略

泰拉瑞亚狐狸套装(动物学家)怎么得 狐狸套装获取攻略

泰拉瑞亚冰冻海龟壳怎么获得有什么用 冰冻海龟壳可以合成什么

泰拉瑞亚冰冻海龟壳怎么获得有什么用 冰冻海龟壳可以合成什么

泰拉瑞亚葬礼套装如何获得 葬礼套装获取方式分享

泰拉瑞亚葬礼套装如何获得 葬礼套装获取方式分享

泰拉瑞亚英雄护盾怎么获得 英雄护盾效果

泰拉瑞亚英雄护盾怎么获得 英雄护盾效果

泰拉瑞亚熔岩护身符怎么弄 熔岩护身符可以合成什么

泰拉瑞亚熔岩护身符怎么弄 熔岩护身符可以合成什么

泰拉瑞亚黑曜石护盾怎么做有什么用 黑曜石护盾可以合成什么

泰拉瑞亚黑曜石护盾怎么做有什么用 黑曜石护盾可以合成什么

泰拉瑞亚圣骑士护盾怎么获得好用吗 圣骑士护盾可以合成什么

泰拉瑞亚圣骑士护盾怎么获得好用吗 圣骑士护盾可以合成什么

泰拉瑞亚脚镣怎么得有什么用 脚镣可以合成什么

泰拉瑞亚脚镣怎么得有什么用 脚镣可以合成什么

泰拉瑞亚星星面纱怎么获得 星星面纱合成什么好

泰拉瑞亚星星面纱怎么获得 星星面纱合成什么好

泰拉瑞亚蠕虫围巾怎么获得 蠕虫围巾效果可以叠加吗

泰拉瑞亚蠕虫围巾怎么获得 蠕虫围巾效果可以叠加吗

泰拉瑞亚再生手环怎么得 再生手环可以叠加吗

泰拉瑞亚再生手环怎么得 再生手环可以叠加吗

泰拉瑞亚神话护身符怎么样 神话护身符什么属性最好

泰拉瑞亚神话护身符怎么样 神话护身符什么属性最好

泰拉瑞亚点金石怎么得 点金石在哪刷

泰拉瑞亚点金石怎么得 点金石在哪刷

泰拉瑞亚闪亮石怎么获得 闪亮石可以合成什么

泰拉瑞亚闪亮石怎么获得 闪亮石可以合成什么

泰拉瑞亚掘墓者套装效果 掘墓者套装怎么获得

泰拉瑞亚掘墓者套装效果 掘墓者套装怎么获得

泰拉瑞亚英雄套装怎么得 英雄套装效果

泰拉瑞亚英雄套装怎么得 英雄套装效果

泰拉瑞亚拉弥亚服装怎么得 拉弥亚套装介绍

泰拉瑞亚拉弥亚服装怎么得 拉弥亚套装介绍

泰拉瑞亚蜥蜴套装怎么得 蜥蜴套装分享

泰拉瑞亚蜥蜴套装怎么得 蜥蜴套装分享

泰拉瑞亚女仆套装怎么做 女仆套装介绍

泰拉瑞亚女仆套装怎么做 女仆套装介绍

泰拉瑞亚1.4女仆装怎么获得 粉女仆套装介绍

泰拉瑞亚1.4女仆装怎么获得 粉女仆套装介绍

泰拉瑞亚大师级玩家套装效果 大师级玩家套装介绍

泰拉瑞亚大师级玩家套装效果 大师级玩家套装介绍

泰拉瑞亚美人鱼套装怎么得 美人鱼套装有什么用

泰拉瑞亚美人鱼套装怎么得 美人鱼套装有什么用

泰拉瑞亚木乃伊套装效果 木乃伊套装怎么得

泰拉瑞亚木乃伊套装效果 木乃伊套装怎么得

泰拉瑞亚奥术花怎么获得 奥术花合成方法

泰拉瑞亚奥术花怎么获得 奥术花合成方法

泰拉瑞亚星力手环怎么获得 星力手环能合成什么

泰拉瑞亚星力手环怎么获得 星力手环能合成什么

泰拉瑞亚天界手铐如何获得 天界手铐和天界徽章哪个好

泰拉瑞亚天界手铐如何获得 天界手铐和天界徽章哪个好

泰拉瑞亚天界磁石怎么得有什么用 天界磁石有必要买吗

泰拉瑞亚天界磁石怎么得有什么用 天界磁石有必要买吗

泰拉瑞亚魔法手铐怎么获得有什么用 魔法手铐可以合成什么

泰拉瑞亚魔法手铐怎么获得有什么用 魔法手铐可以合成什么

泰拉瑞亚磁花有什么用能合成什么 磁花和奥秘花那个好

泰拉瑞亚磁花有什么用能合成什么 磁花和奥秘花那个好

泰拉瑞亚魔力斗篷怎么做有什么用 魔力斗篷和星星面纱哪个好

泰拉瑞亚魔力斗篷怎么做有什么用 魔力斗篷和星星面纱哪个好

泰拉瑞亚钥匙大全 钥匙怎么获得有什么用分享

泰拉瑞亚钥匙大全 钥匙怎么获得有什么用分享

泰拉瑞亚魔力花怎么做有什么用 魔力花升级什么最好

泰拉瑞亚魔力花怎么做有什么用 魔力花升级什么最好

泰拉瑞亚魔力再生手环怎么获得有什么用 魔力再生手环可以合成什么

泰拉瑞亚魔力再生手环怎么获得有什么用 魔力再生手环可以合成什么

泰拉瑞亚大自然的恩赐怎么获得有什么用 大自然的恩赐有多少几率掉

泰拉瑞亚大自然的恩赐怎么获得有什么用 大自然的恩赐有多少几率掉

泰拉瑞亚松露虫怎么抓 松露虫生成条件是什么

泰拉瑞亚松露虫怎么抓 松露虫生成条件是什么

泰拉瑞亚雏翼怎么升级有什么用 雏翼怎么飞

泰拉瑞亚雏翼怎么升级有什么用 雏翼怎么飞

泰拉瑞亚挖矿盔甲怎么获得 挖矿盔甲套装属性怎么样

泰拉瑞亚挖矿盔甲怎么获得 挖矿盔甲套装属性怎么样

泰拉瑞亚天使之翼怎么合成 天使之翼和恶魔之翼哪个好

泰拉瑞亚天使之翼怎么合成 天使之翼和恶魔之翼哪个好

泰拉瑞亚恶魔之翼怎么合成怎么做 恶魔之翼和鸟妖之翼哪个好

泰拉瑞亚恶魔之翼怎么合成怎么做 恶魔之翼和鸟妖之翼哪个好

泰拉瑞亚蘑菇套装有什么用 蘑菇套装好用吗

泰拉瑞亚蘑菇套装有什么用 蘑菇套装好用吗